1 overview, Overview, Table 1: ip core main features – BECKHOFF EtherCAT IP Core for Altera FPGAs v3.0.10 User Manual

Page 13: Figure 1: ethercat ip core block diagram

Overview

Slave Controller

– IP Core for Altera FPGAs

III-1

1

Overview

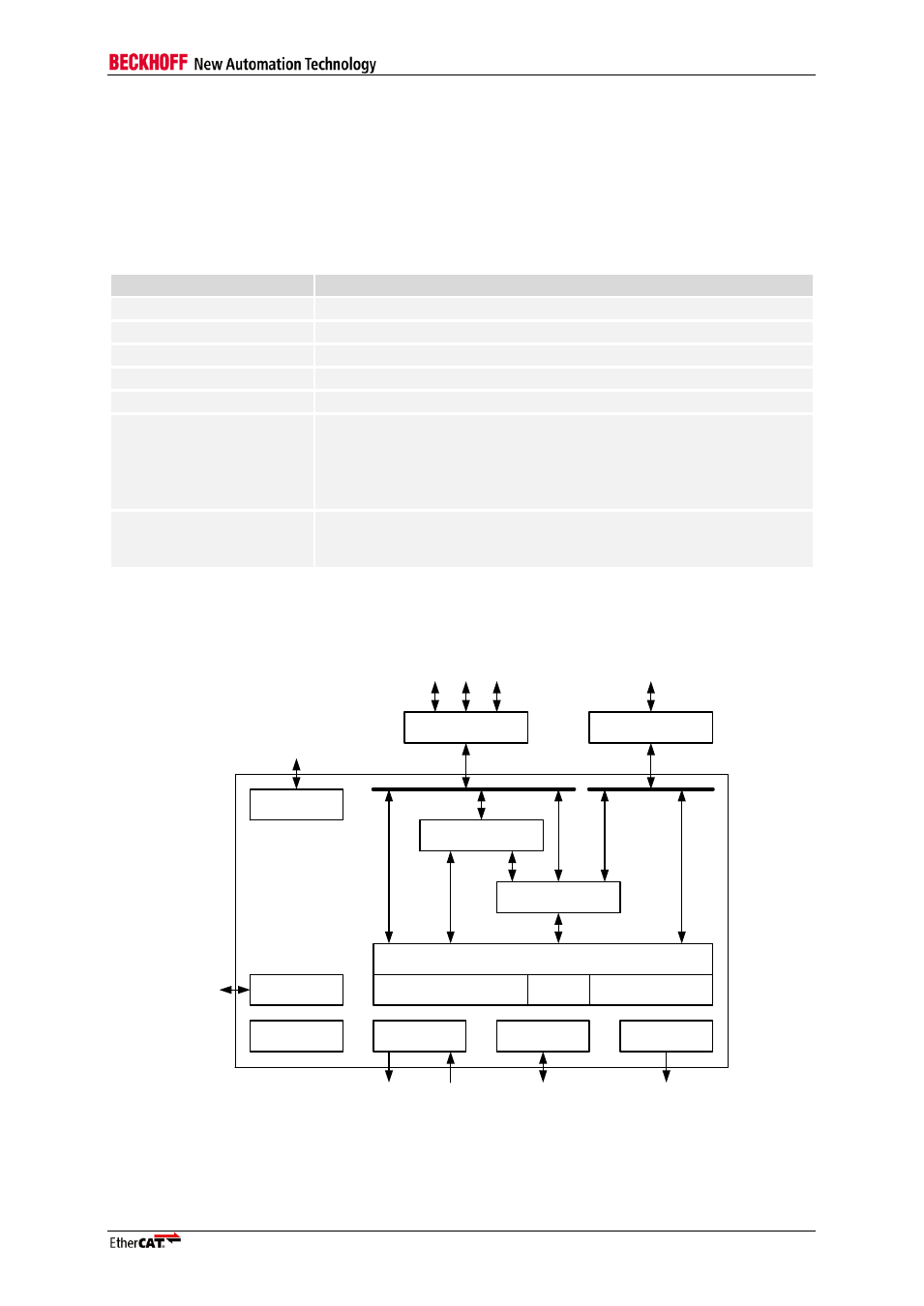

The EtherCAT IP Core is a configurable EtherCAT Slave Controller (ESC). It takes care of the

EtherCAT communication as an interface between the EtherCAT fieldbus and the slave application.

The EtherCAT IP Core is delivered as a configurable system so that the feature set fits the

requirements perfectly and brings costs down to an optimum.

Table 1: IP Core Main Features

Feature

IP Core configurable features

Ports

1-3 MII ports or 1-3 RGMII ports 1-2 RMII ports

FMMUs

0-8

SyncManagers

0-8

RAM

0-60 KB

Distributed Clocks

Yes, 32 bit or 64 bit

Process Data Interfaces

32 Bit Digital I/O (unidirectional)

SPI Slave

8/16 bit asynchronous µController Interface

Avalon

®

on-chip bus

AMBA

®

AXI3

TM

on-chip bus

Other features

Example designs for easy start up included

Slave applications can run on-chip if the appropriate FPGAs with

sufficient resources are used

The general functionality of the EtherCAT IP Core is shown in Figure 1:

ECAT

Processing

Unit

AutoForwarder +

Loopback

SyncManager

FMMU

ESC address space

User RAM

Registers

Process RAM

EEPROM

Distributed

Clocks

Monitoring

Status

PHY

Management

SYNC

LEDs

I²C EEPROM

PHY MI

SPI / µC / Digital I/O /

Avalon / AXI3

0

2

MII ports

LATCH

PDI

ECAT Interface

PDI Interface

1

Reset

Reset

Figure 1: EtherCAT IP Core Block Diagram