The dtw_timing_analysis.tcl script results, Notes (1) – Altera DDR Timing Wizard User Manual

Page 66

3–6

Altera Corporation

DDR Timing Wizard User Guide

November 2007

Introduction

4.

Open the Compilation Report panel by clicking on Compilation

Report

under the Processing menu. If the Compilation Report

panel is open, you have to close it and reopen it.

The dtw_timing_analysis.tcl script appends its result onto the

Compilation Report, and is automatically displayed after refreshing

the Compilation Report panel.

The dtw_timing_analysis.tcl Script Results

The script result is added at the bottom of the compilation result as

Memory Interface Timing

with the name of the controller and .dwz file

in parentheses under that folder, and shows the script result with my_core

(ddr_settings.dwz), because the controller’s name is my_core and the

.dwz

file name used to constrain the memory interface timing is called

ddr_settings.dwz

, as shown in

.

-stop_after

Any integer

Indicates the maximum number of

iterations when using the

-auto_adjust_cycles

switch to

prevent infinite iterations. The default

value is 5.

No

-vwf_file_name

A .vwf file name

Creates a waveform showing the

interface timing margin in a .vwf

format.

No

-write_side

●

tanrpt

●

tq

●

skip

●

auto

Tells the script whether you want to

use Classic or TimeQuest Timing

Analyzer for the write side timing

analysis. You also have the option to

skip write timing analysis. The default

is TimeQuest Timing Analyzer,

regardless of what timing analyzer

was used in the design. Classic timing

analyzer is not recommended for write

timing analysis.

No

(1)

Fedback clock in this implementation is used for read capture, not for resynchronization.

(2)

RLDRAM II and QDRII+/QDRII SRAM interfaces do not require resynchronization clocks, as the Altera IP MegaCore

functions use a FIFO to resynchronize data to system clock.

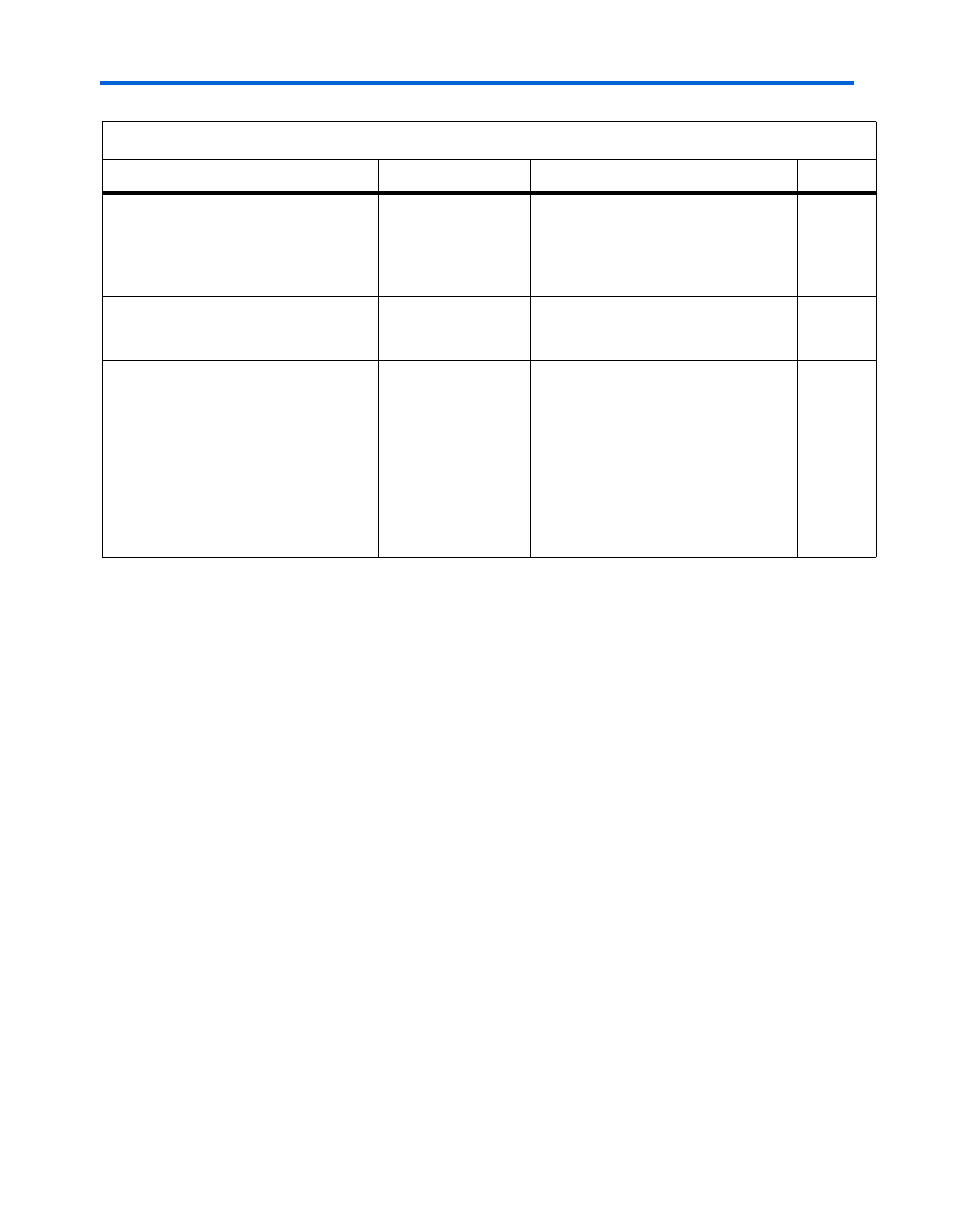

Table 3–1. Switches in the dtw_timing_analysis.tcl Script (Part 4 of 4)

Notes (1)

,

(2)

Switch

Possible Value

Description

Required