Read dma avalon-mm master port, Read dma avalon-mm master port -3 – Altera Arria 10 Avalon-MM DMA User Manual

Page 44

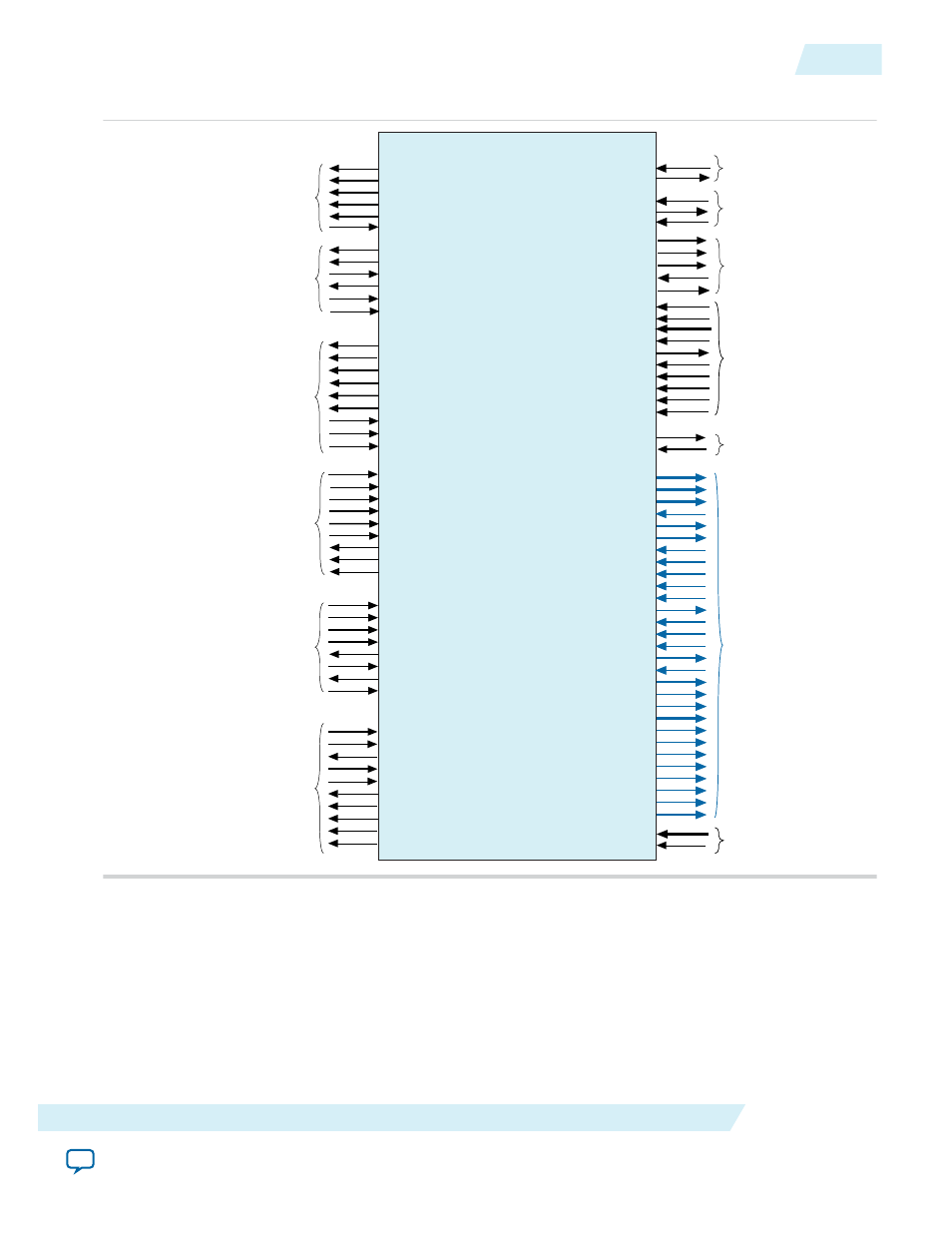

Figure 5-2: Signals When DMA Descriptor Controller Is Instantiated Externally

tx_out0[

rx_in0[

Serial Data

Hard IP for PCI Express Using Avalon-MM with DMA

TxsWriteData_i[31:0]

TxsRead_i

TxsWrite_i

TxsChipSelect_i

TxsAddress_i[

TxsByteEnable[3:0]

TxsReadData_o[31:0]

TxsReadDataValid_o

TxsWaitRequest_o

TX (CRA) Slave:

Allows FPGA to send single

dword reads or writes

from FPGA to Root Port

RxmRead_o

RxmWrite_o

RxmAddress_o[

RxmBurstCount_o[5:0]

RxmByteEnable_o[3:0]

RxmWriteData_o[31:0]

RxmReadData_i[31:0]

RxmReadDataValid_i

RxmWaitRequest_i

CraWriteData_i[31:0]

CraWaitRequest_o

CraChipSelect_i

CraByteEnable_i[3:0]

CraAddress_i[13:0]

CraRead_i

CraWrite_i

CraReadData_o[31:0]

Local Avalon-MM or

Host Access to

Control/Status Regs

of Avalon-MM Bridge

RdDmaWrite_o

RdDmaAddress_o[63:0]

RdDmaWriteData[

RdDmaBurstCount_o[

RdDmaByteEnable_o[

RdDmaWaitRequest_i

DMA Read Avalon-MM :

Writes data from Host

memory to FPGA memory.

WrDmaRead_o

WrDmaAddress_o[63:0]

WrDmaReadData_i[

WrDmaBurstCount_o[

WrDmaWaitRequest_i

WrDmaReadDataValid_i

DMA Write Avalon-MM :

Fetch data from FPGA memory

before sending to Host memory.

npor

nreset_status

pin_perst

Reset &

Lock Status

Clocks

refclk

coreclkout_hip

Avalon-MM Master

for Host to access

registers and memory

1 RX Master for each

BAR

test_in[31:0]

simu_mode_pipe

Host or

RdAstRxData_i[159:0]

RdAstRxValid_i

RdAstRxReady_o

WrAstRxData_i[159:0]

WrAstRxValid_i

WrAstRxReady_o

WrAstTxData_o[31:0]

WrAstTxValid_o

Descriptor Instructions

from

Descriptor Controller

to DMA Engine

RdAstTxData_o[31:0]

RdAstTxValid_o

Gen3 PIPE

(simulation

only)

currentcoeff0[17:0]

currentrxpreset0[2:0]

eidleinfersel[2:0]

phystatus0

powerdown0[1:0]

rate[1:0]

rxblkst0

rxdata0[31:0]

rxdatak[3:0]

rxdataskip

rxelecidle0

rxpolarity

rxstatus0[2:0]

rxsynchd0[1:0]

rxvalid0

sim_ltssmstate[4:0]

sim_pipe_pclk_in

sim_pipe_rate[1:0]

txblkst

txcompl0

txdata[31:0]

txdatak0

txdataskip

txdeemph0

txdetectrx0

txelecidle0

txmargin0

txswing0

txsynchd0[1:0]

MsiIntfc_o[81:0]

MsixIntfc_o[15:0]

MsiControl_o[15:0]

intx_req_i

intx_ack_o

MSI and MSI-X

Interface

Hard IP

Reconfiguration

(Optional)

hip_reconfig_clk

hip_reconfig_rst_n

hip_reconfig_address[9:0]

hip_reconfig_read

hip_reconfig_readdata[15:0]

hip_reconfig_write

hip_reconfig_writedata[15:0]

hip_reconfig_byte_en[1:0]

ser_shift_load

interface_sel

Test and

Mode Control

Read DMA Avalon-MM Master Port

The Read DMA module sends memory read TLPs upstream. It writes the completion data to an external

Avalon-MM interface through the high throughput Read Master port. This port operates on descriptors

the IP core receives from the DMA Descriptor Controller.

UG-01145_avmm_dma

2015.05.14

Read DMA Avalon-MM Master Port

5-3

IP Core Interfaces

Altera Corporation