Link capabilities, Msi and msi-x capabilities, Link capabilities -11 – Altera Arria 10 Avalon-MM DMA User Manual

Page 31: Msi and msi-x capabilities -11

Parameter

Value

Default Value

Description

Note:

1. Throughout this user guide, the terms word, dword and qword have the same meaning that they have

in the PCI Express Base Specification. A word is 16 bits, a dword is 32 bits, and a qword is 64 bits.

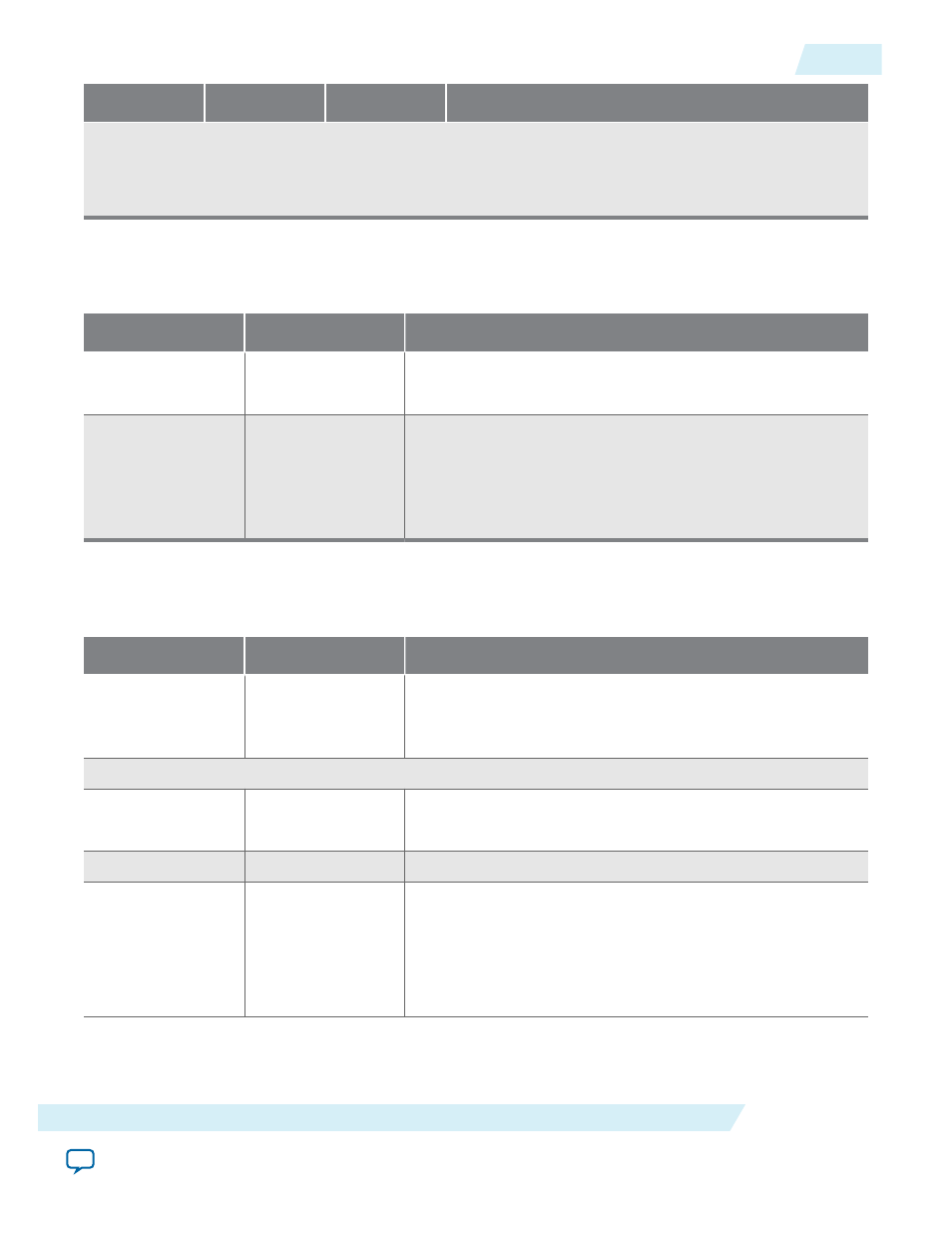

Link Capabilities

Table 3-7: Link Capabilities

Parameter

Value

Description

Link port

number

0x01

Sets the read-only value of the port number field in the

Link

Capabilities

register.

Slot clock

configuration

On/Off

When On, indicates that the Endpoint or Root Port uses the

same physical reference clock that the system provides on the

connector. When Off, the IP core uses an independent clock

regardless of the presence of a reference clock on the

connector.

MSI and MSI-X Capabilities

Table 3-8: MSI and MSI-X Capabilities

Parameter

Value

Description

MSI messages

requested

1, 2, 4, 8, 16, 32

Specifies the number of messages the Application Layer can

request. Sets the value of the

Multiple Message Capable

field of the

Message Control

register, 0x050[31:16].

MSI-X Capabilities

Implement MSI-

X

On/Off

When On, enables the MSI-X functionality.

Bit Range

Table size

[10:0]

System software reads this field to determine the MSI-X Table

size

value of 2047 indicates a table size of 2048. This field is read-

only. Legal range is 0–2047 (2

11

).

Address offset: 0x068[26:16]

UG-01145_avmm_dma

2015.05.14

Link Capabilities

3-11

Parameter Settings

Altera Corporation