Understanding the simulation generated files, Understanding simulation log file generation, Simulating the example design in modelsim – Altera Arria 10 Avalon-MM DMA User Manual

Page 17: Understanding the simulation generated files -4, Understanding simulation log file generation -4, Simulating the example design in modelsim -4

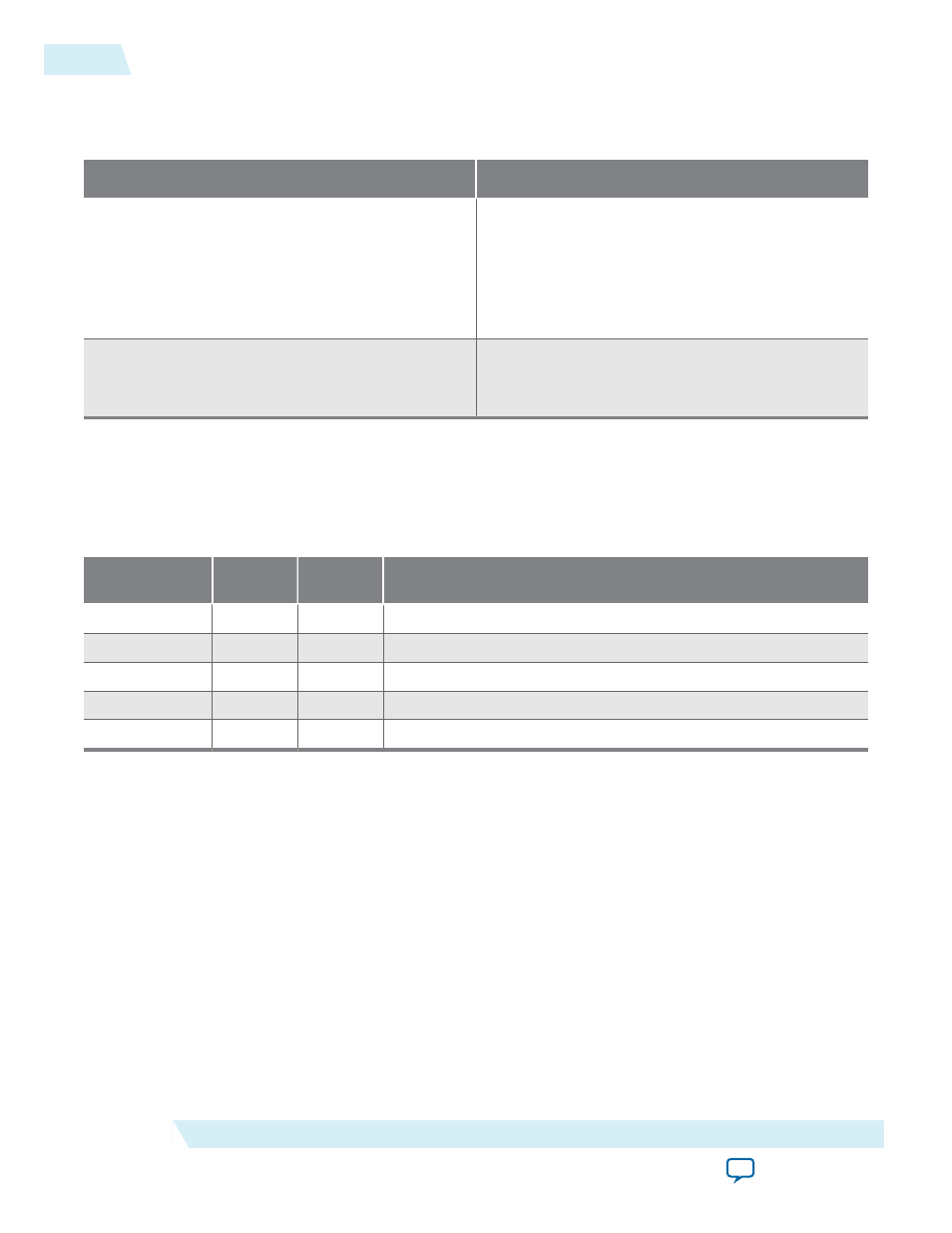

Understanding the Simulation Generated Files

Table 2-2: Qsys Generation Output Files

Directory

Description

g3x8_avmm256_integrated_tb/

Includes directories for all components of the

testbench. Also includes the following files:

• Simulation Package Descriptor File (

.spd

) which

lists the required simulation files

• Comma-Separated Value File (

.csv

) describing

the files in the testbench

g3x8_avmm256_integrated_tb/sim/

Includes testbench subdirectories for the Aldec,

Cadence, Mentor, and Synopsys simulation tools

with the required libraries and simulation scripts.

Understanding Simulation Log File Generation

Starting with the Quartus II 14.0 software release, simulation automatically creates a log file,

altpcie_

monitor_

in your simulation directory.

Table 2-3: Sample Simulation Log File Entries

Time

TLP Type

Payload

(Bytes)

TLP Header

17989 RX

CfgRd0

0004

04000001_0000000F_01080008

17989 RX

MRd

0000

00000000_00000000_01080000

18021 RX

CfgRd0

0004

04000001_0000010F_0108002C

18053 RX

CfgRd0

0004

04000001_0000030F_0108003C

18085 RX

MRd

0000

00000000_00000000_0108000C

Simulating the Example Design in ModelSim

1. In a terminal, change directory to

sim/mentor

.

2. Start the ModelSim

®

simulator.

3. To run the simulation, type the following commands in a terminal window:

a.

do msim_setup.tcl

b.

ld_debug

The

ld_debug

command compiles all design files and elaborates the top-level design without any

optimization.

c.

run -all

The simulation performs the following operations:

2-4

Understanding the Simulation Generated Files

UG-01145_avmm_dma

2015.05.14

Altera Corporation

Getting Started with the Avalon-MM DMA