Altera SCFIFO User Manual

Page 9

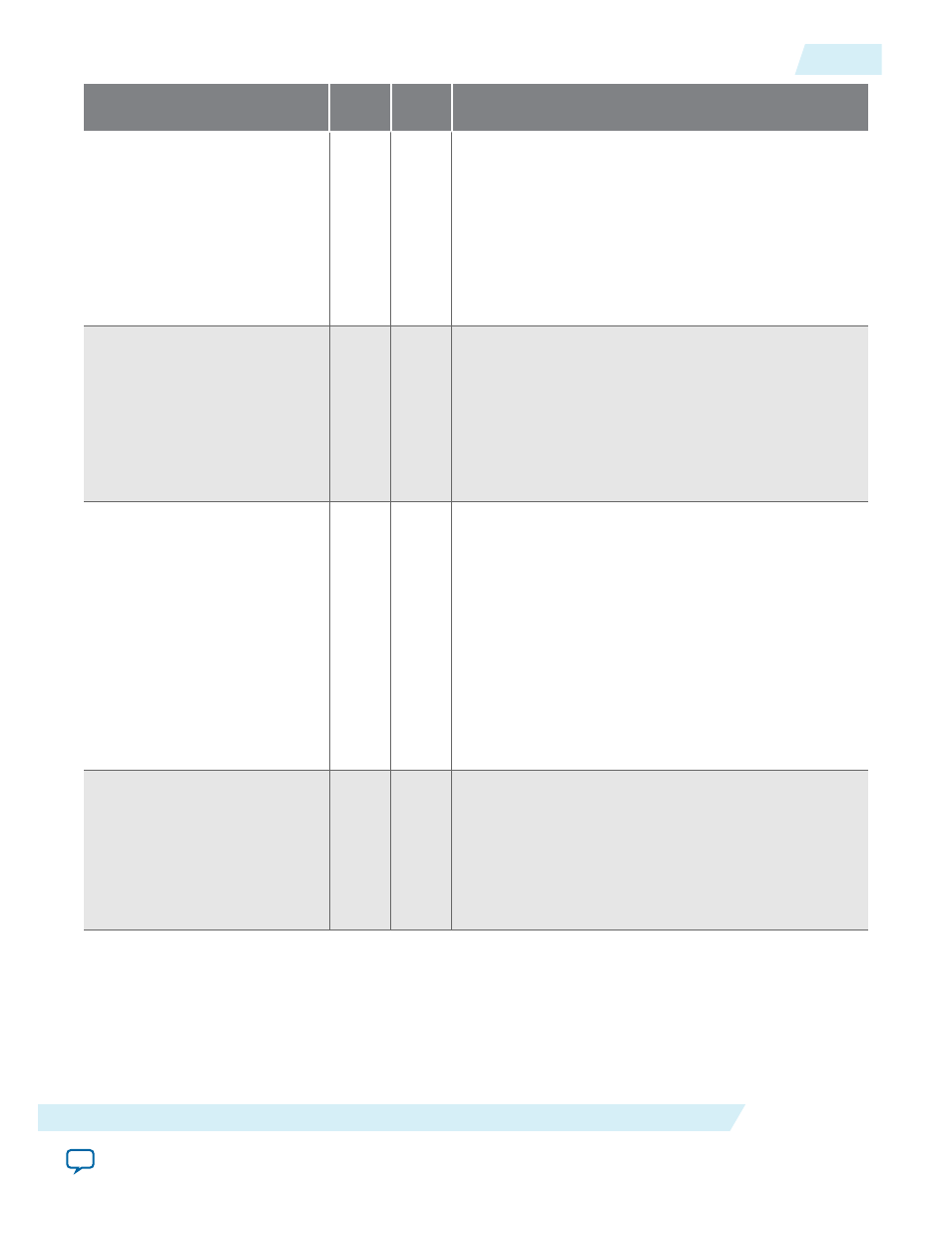

Parameter

Type

Requir

ed

Description

write_aclr_synch

(5)

String

No

Specifies whether or not to add a circuit that causes the

aclr

port to be internally synchronized by the

wrclk

clock. Adding the circuit prevents the race condition

between the

wrreq

and

aclr

ports that could corrupt

the FIFO IP core.

The values are ON or OFF. If omitted, the default value

is

OFF

. This parameter is only applicable for Stratix and

Cyclone series (except for Stratix, Stratix GX, and

Cyclone devices).

read_aclr_synch

String

No

Specifies whether or not to add a circuit that causes the

aclr

port to be internally synchronized by the

rdclk

clock. Adding the circuit prevents the race condition

between the

rdreq

and

aclr

ports that could corrupt

the FIFO IP core.

The values are ON or OFF. If omitted, the default value

is OFF. This parameter is only applicable for families

beginning from Stratix III series.

clocks_are_synchron-

ized

(5)

String

No

Specifies whether or not the write and read clocks are

synchronized which in turn determines the number of

internal synchronization stages added for stable

operation of the FIFO. The values are TRUE and

FALSE. If omitted, the default value is FALSE. You

must only set the parameter to TRUE if the write clock

and the read clock are always synchronized and they

are multiples of each other. Otherwise, set this to

FALSE to avoid metastability problems.

If the clocks are not synchronized, set the parameter to

FALSE, and use the

rdsync_delaypipe

and

wrsync_

delaypipe

parameters to determine the number of

synchronization stages required.

ram_block_type

String

No

Specifies the target device’s Trimatrix Memory Block to

be used. To get the proper implementation based on

the RAM configuration that you set, allow the

Quartus II software to automatically choose the

memory type by ignoring this parameter and set the

use_eab

parameter to ON. This gives the compiler the

flexibility to place the memory function in any available

memory resource based on the FIFO depth required.

UG-MFNALT_FIFO

2014.12.17

SCFIFO and DCFIFO Parameters

9

SCFIFO and DCFIFO IP Cores User Guide

Altera Corporation