Different input and output width – Altera SCFIFO User Manual

Page 18

Recovery and Removal Timing Violation Warnings when Compiling a DCFIFO IP

Core

During compilation of a design that contains a DCFIFO IP core, the Quartus II software may issue

recovery and removal timing violation warnings.

You may safely ignore warnings that represent transfers from

aclr

to the read side clock domain. To

ensure that the design meets timing, enable the ACLR synchronizer for both read and write domains.

To enable the ACLR synchronizer for both read and write domains, on the DCFIFO 2 tab of the FIFO

MegaWizard Plug-In Manager, turn on Asynchronous clear, Add circuit to synchronize ‘aclr’ input

with ‘wrclk’, and Add circuit to synchronize ‘aclr’ input with ‘rdclk’.

Note: For correct timing analysis, Altera recommends enabling the Removal and Recovery Analysis

option in the TimeQuest timing analyzer tool when you use the

aclr

signal. The analysis is turned

on by default in the TimeQuest timing analyzer tool.

Different Input and Output Width

The DCFIFO_MIXED_WIDTHS IP core supports different write input data and read output data widths

if the width ratio is valid. The FIFO parameter editor prompts an error message if the combinations of the

input and the output data widths produce an invalid ratio. The supported width ratio in a power of 2 and

depends on the RAM.

The IP core supports a wide write port with a narrow read port, and vice versa.

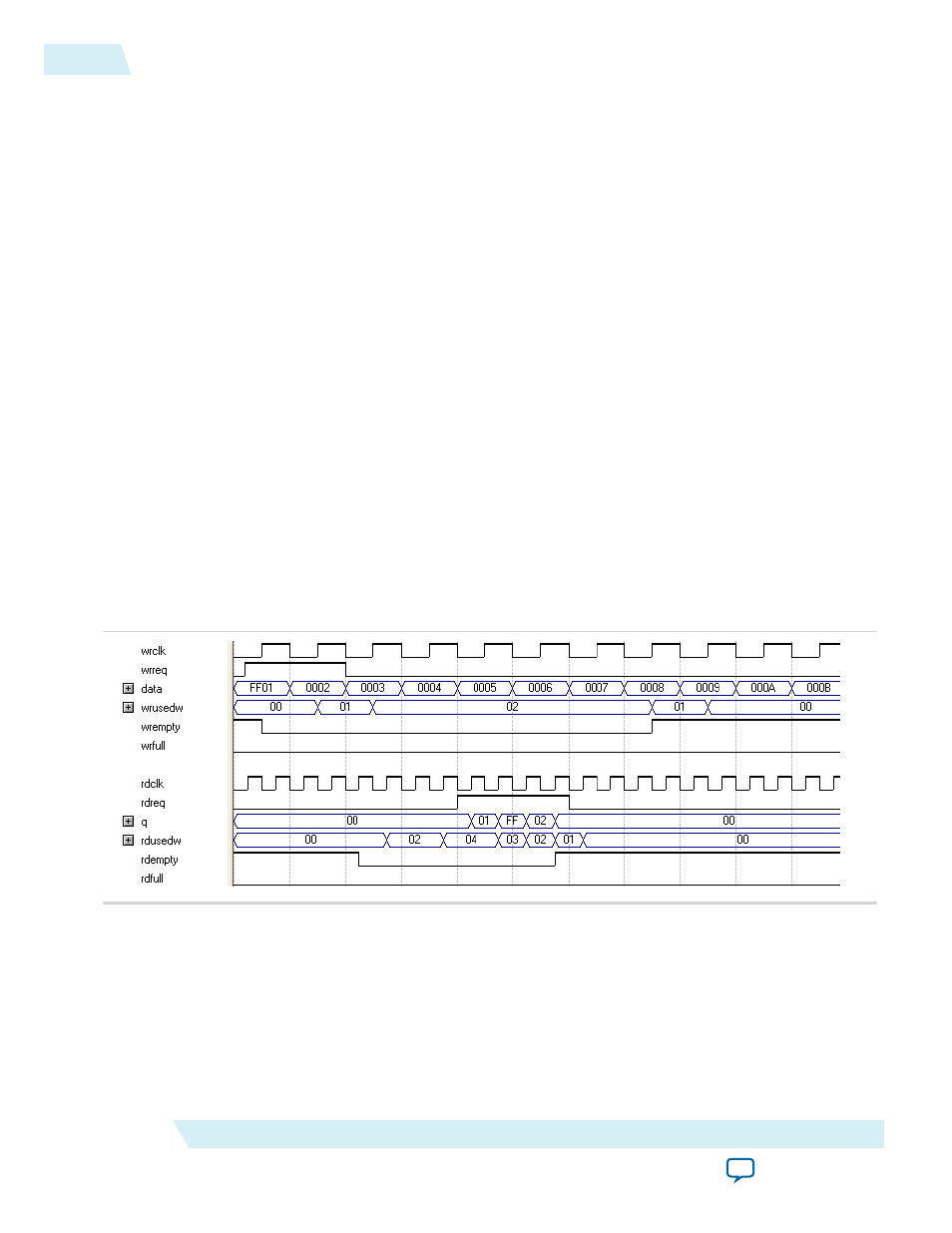

Figure 4: Writing 16-bit Words and Reading 8-bit Words

This figure shows an example of a wide write port (16-bit input) and a narrow read port (8-bit output).

In this example, the read port is operating at twice the frequency of the write port. Writing two 16-bit

words to the FIFO buffer increases the

wrusedw

flag to two and the

rusedw

flag to four. Four 8-bit read

operations empty the FIFO buffer. The read begins with the least-significant 8 bits from the 16-bit word

written followed by the most-significant 8 bits.

18

Recovery and Removal Timing Violation Warnings when Compiling a DCFIFO IP Core

UG-MFNALT_FIFO

2014.12.17

Altera Corporation

SCFIFO and DCFIFO IP Cores User Guide