Altera SCFIFO User Manual

Page 3

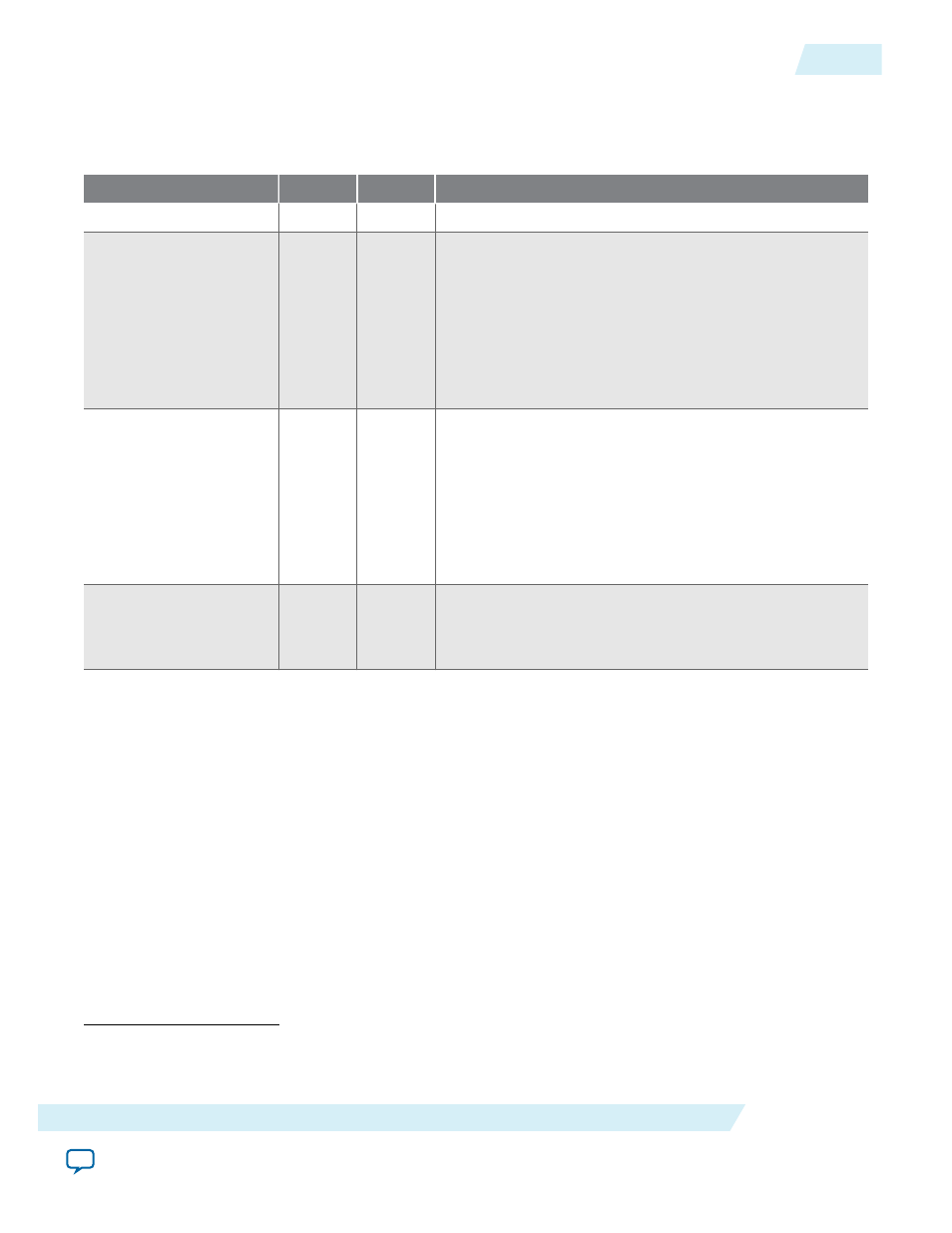

Table 2: Input and Output Ports Description

This table lists the signals of the IP cores. The term “series” refers to all the device families of a particular device.

For example, “Stratix series” refers to the Stratix

®

, Stratix GX, Stratix II, Stratix II GX, Stratix III, and new devices,

unless specified otherwise.

Port

Type

Required

Description

clock

(1)

Input

Yes

Positive-edge-triggered clock.

wrclk

(2)

Input

Yes

Positive-edge-triggered clock.

Use to synchronize the following ports:

•

data

•

wrreq

•

wrfull

•

wrempty

•

wrusedw

rdclk

(2)

Input

Yes

Positive-edge-triggered clock.

Use to synchronize the following ports:

•

q

•

rdreq

•

rdfull

•

rdempty

•

rdusedw

data

(3)

Input

Yes

Holds the data to be written in the FIFO IP core when the

wrreq

signal is asserted. If you manually instantiate the

FIFO IP core, ensure the port width is equal to the

lpm_

width

parameter.

(1)

Only applicable for the SCFIFO IP core.

(2)

Applicable for both of the DCFIFO IP cores.

(3)

Applicable for the SCFIFO, DCFIFO, and DCFIFO_MIXED_WIDTH IP cores.

UG-MFNALT_FIFO

2014.12.17

SCFIFO and DCFIFO Signals

3

SCFIFO and DCFIFO IP Cores User Guide

Altera Corporation