Altera SCFIFO User Manual

Page 8

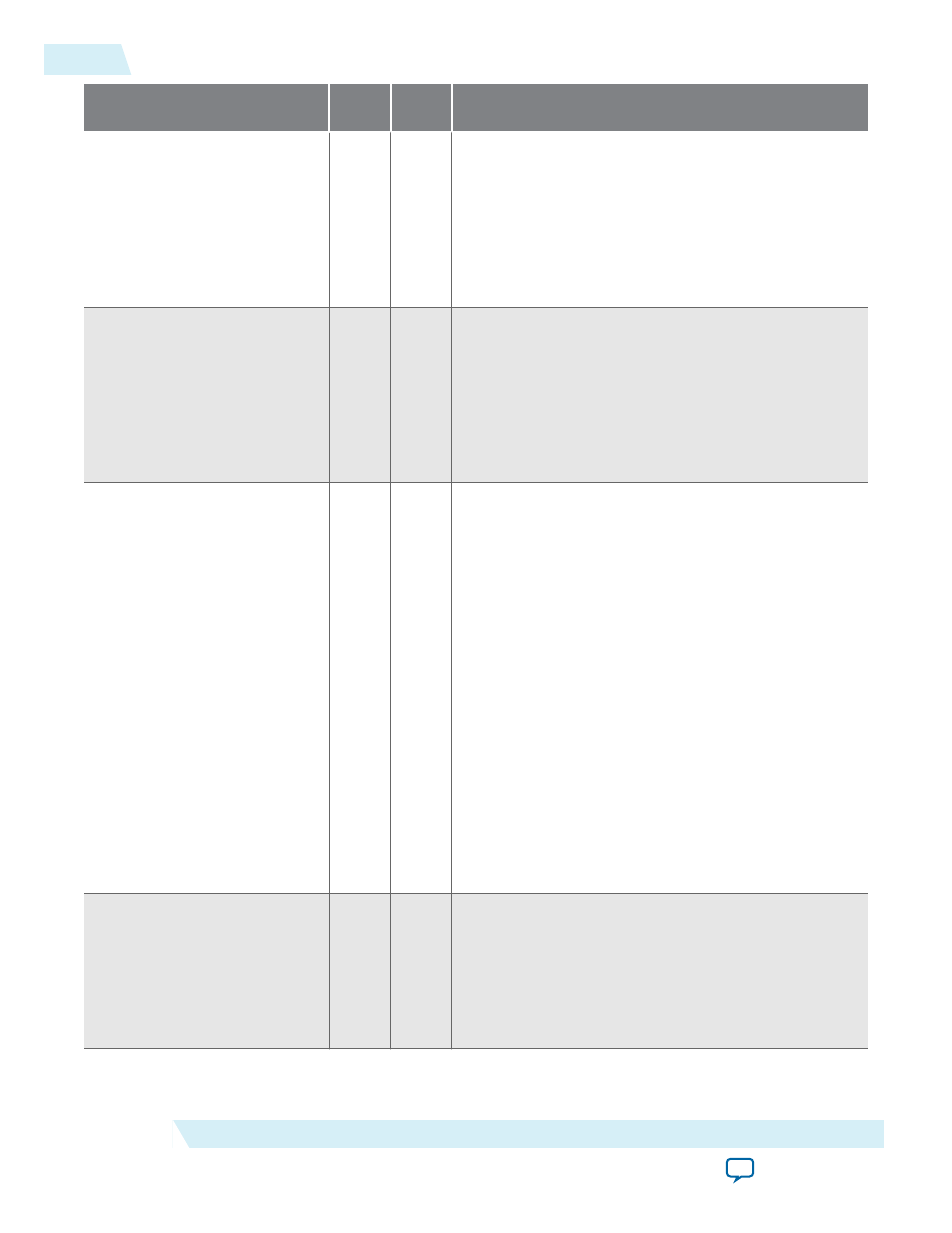

Parameter

Type

Requir

ed

Description

delay_rdusedw

(5)

delay_wrusedw

(5)

String

No

Specify the number of register stages that you want to

internally add to the

rdusedw

or

wrusedw

port using

the respective parameter.

The default value of

1

adds a single register stage to the

output to improve its performance. Increasing the value

of the parameter does not increase the maximum

system speed. It only adds additional latency to the

respective output port.

add_usedw_msb_bit

String

No

Increases the width of the

rdusedw

and

wrusedw

ports

by one bit. By increasing the width, it prevents the

FIFO IP core from rolling over to zero when it is full.

The values are ON or OFF. If omitted, the default value

is OFF.

This parameter is only applicable for Stratix and

Cyclone series (except for Stratix, Stratix GX, and

Cyclone devices).

rdsync_delaypipe

(5)

wrsync_delaypipe

(5)

Integer

No

Specify the number of synchronization stages in the

cross clock domain. The value of the

rdsync_

delaypipe

parameter relates the synchronization

stages from the write control logic to the read control

logic; the

wrsync_delaypipe

parameter relates the

synchronization stages from the read control logic to

the write control logic. Use these parameters to set the

number of synchronization stages if the clocks are not

synchronized, and set the

clocks_are_synchronized

parameter to FALSE.

The actual synchronization stage implemented relates

variously to the parameter value assigned, depends on

the target device.

For Cyclone II and Stratix II devices and later, the

values of these parameters are internally reduced by

two. Thus, the default value of 3 for these parameters

corresponds to a single synchronization stage; a value

of 4 results in two synchronization stages, and so on.

For these devices, choose at least 4 (two synchroniza‐

tion stages) for metastability protection.

use_eab

String

No

Specifies whether or not the FIFO IP core is

constructed using the RAM blocks. The values are ON

or OFF.

Setting this parameter value to OFF yields the FIFO IP

core implemented in logic elements regardless of the

type of the TriMatrix memory block type assigned to

the

ram_block_type

parameter.

8

SCFIFO and DCFIFO Parameters

UG-MFNALT_FIFO

2014.12.17

Altera Corporation

SCFIFO and DCFIFO IP Cores User Guide