Altera SCFIFO User Manual

Page 12

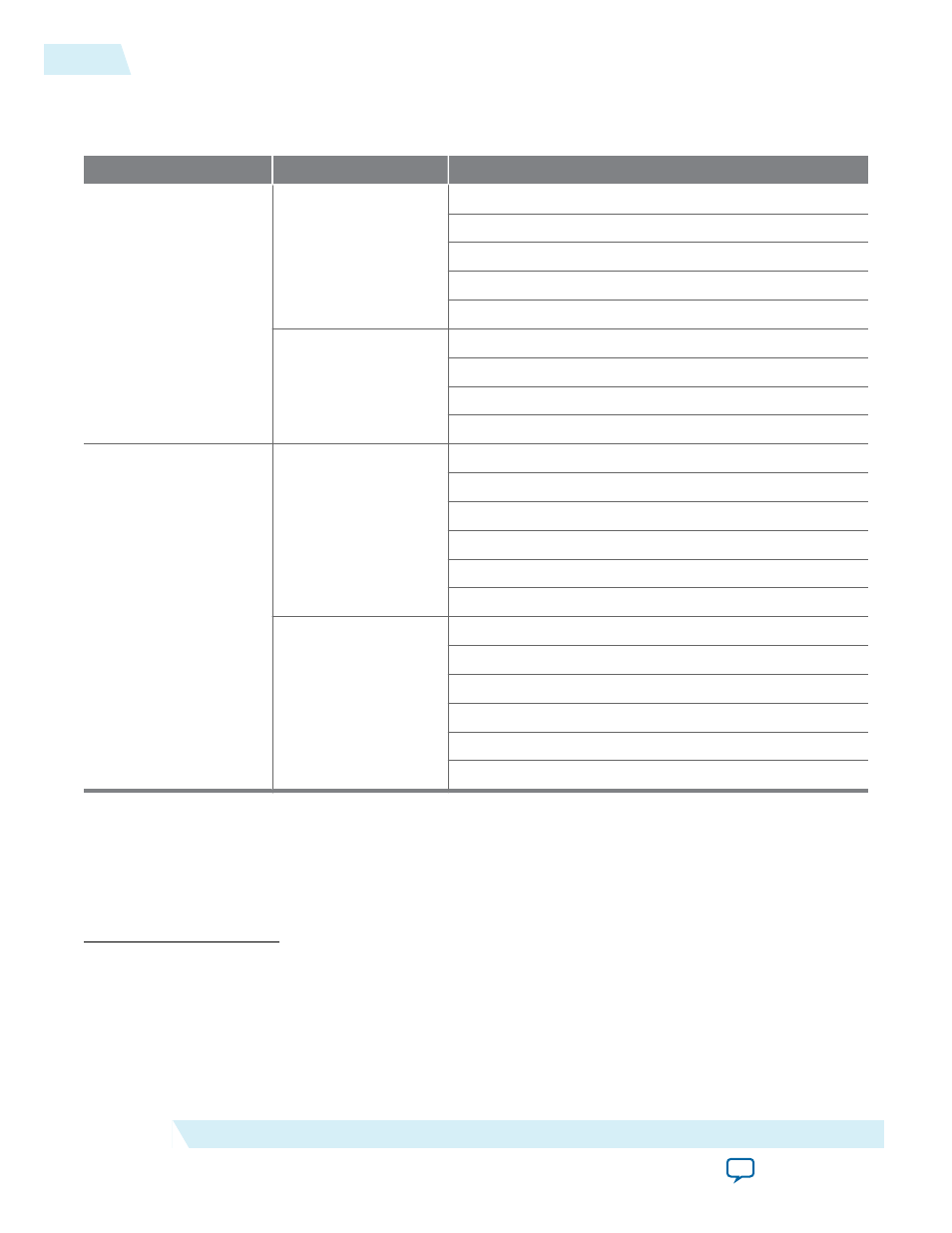

Table 4: Output Latency of the Status Flags for SCFIFO

This table shows the output latency of the write signal (

wrreq

) and read signal (

rdreq

) for the SCFIFO according

to the different output modes and optimization options.

Output Mode

Optimization Option

(7)

Output Latency (in number of clock cycles)

(8)

Normal

(9)

Speed

wrreq

/

rdreq

to

full

: 1

wrreq

to

empty

: 2

rdreq

to

empty

: 1

wrreq

/

rdreq

to

usedw[]

: 1

rdreq

to

q[]

: 1

Area

wrreq

/

rdreq

to

full

: 1

wrreq

/

rdreq

to

empty

: 1

wrreq

/

rdreq

to

usedw[]

: 1

rdreq

to

q[]

: 1

Show-ahead

(9)

Speed

wrreq

/

rdreq

to

full

: 1

wrreq

to

empty

: 3

rdreq

to

empty

: 1

wrreq

/

rdreq

to

usedw[]

: 1

wrreq

to

q[]

: 3

rdreq

to

q[]

: 1

Area

wrreq

/

rdreq

to

full

: 1

wrreq

to

empty

: 2

rdreq

to

empty

: 1

wrreq

/

rdreq

to

usedw[]

: 1

wrreq

to

q[]

: 2

rdreq

to

q[]

: 1

(7)

Speed optimization is equivalent to setting the

ADD_RAM_OUTPUT_REGISTER

parameter to

ON

. Setting the

parameter to

OFF

is equivalent to area optimization.

(8)

The information of the output latency is applicable for Stratix and Cyclone series only. It may not be

applicable for legacy devices such as the APEX

®

and FLEX

®

series.

(9)

For the Quartus II software versions earlier than 9.0, the normal output mode is called legacy output mode.

Normal output mode is equivalent to setting the

LPM_SHOWAHEAD

parameter to

OFF

. For Show-ahead mode,

the parameter is set to

ON

.

12

SCFIFO and DCFIFO Output Status Flag and Latency

UG-MFNALT_FIFO

2014.12.17

Altera Corporation

SCFIFO and DCFIFO IP Cores User Guide