Altera SCFIFO User Manual

Page 4

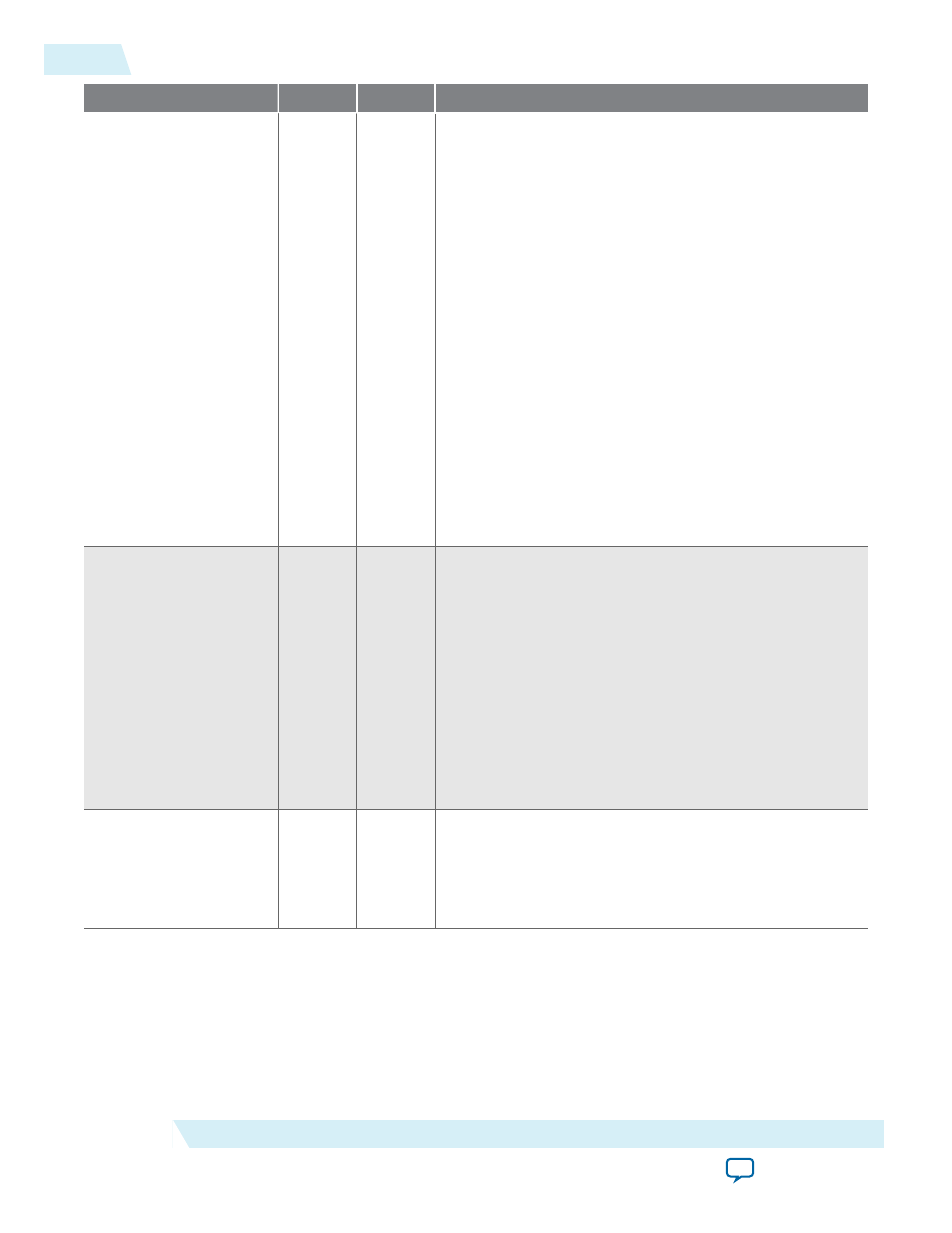

Port

Type

Required

Description

wrreq

(3)

Input

Yes

Assert this signal to request for a write operation.

Ensure that the following conditions are met:

• Do not assert the

wrreq

signal when the

full

(for

SCFIFO) or

wrfull

(for DCFIFO) port is high. Enable

the overflow protection circuitry or set the

overflow_

checking

parameter to ON so that the FIFO IP core

can automatically disable the

wrreq

signal when it is

full.

• The

wrreq

signal must meet the functional timing

requirement based on the

full

or

wrfull

signal.

• Do not assert the

wrreq

signal during the deassertion

of the

aclr

signal. Violating this requirement creates a

race condition between the falling edge of the

aclr

signal and the rising edge of the write clock if the

wrreq

port is set to high. For both the DCFIFO IP

cores that target Stratix and Cyclone series (except

Stratix, Stratix GX, and Cyclone devices), you have the

option to automatically add a circuit to synchronize

the

aclr

signal with the

wrclk

clock, or set the

write_

aclr_synch

parameter to ON. Use this option to

ensure that the restriction is obeyed.

rdreq

(3)

Input

Yes

Assert this signal to request for a read operation. The

rdreq

signal acts differently in normal mode and show-

ahead mode.

Ensure that the following conditions are met:

• Do not assert the

rdreq

signal when the

empty

(for

SCFIFO) or

rdempty

(for DCFIFO) port is high.

Enable the underflow protection circuitry or set the

underflow_checking

parameter to ON so that the

FIFO IP core can automatically disable the

rdreq

signal when it is empty.

• The

rdreq

signal must meet the functional timing

requirement based on the

empty

or

rdempty

signal.

sclr

(1)

aclr

(3)

Input

No

Assert this signal to clear all the output status ports, but

the effect on the

q

output may vary for different FIFO

configurations.

There are no minimum number of clock cycles for

aclr

signals that must remain active.

4

SCFIFO and DCFIFO Signals

UG-MFNALT_FIFO

2014.12.17

Altera Corporation

SCFIFO and DCFIFO IP Cores User Guide