Scfifo and dcfifo output status flag and latency – Altera SCFIFO User Manual

Page 11

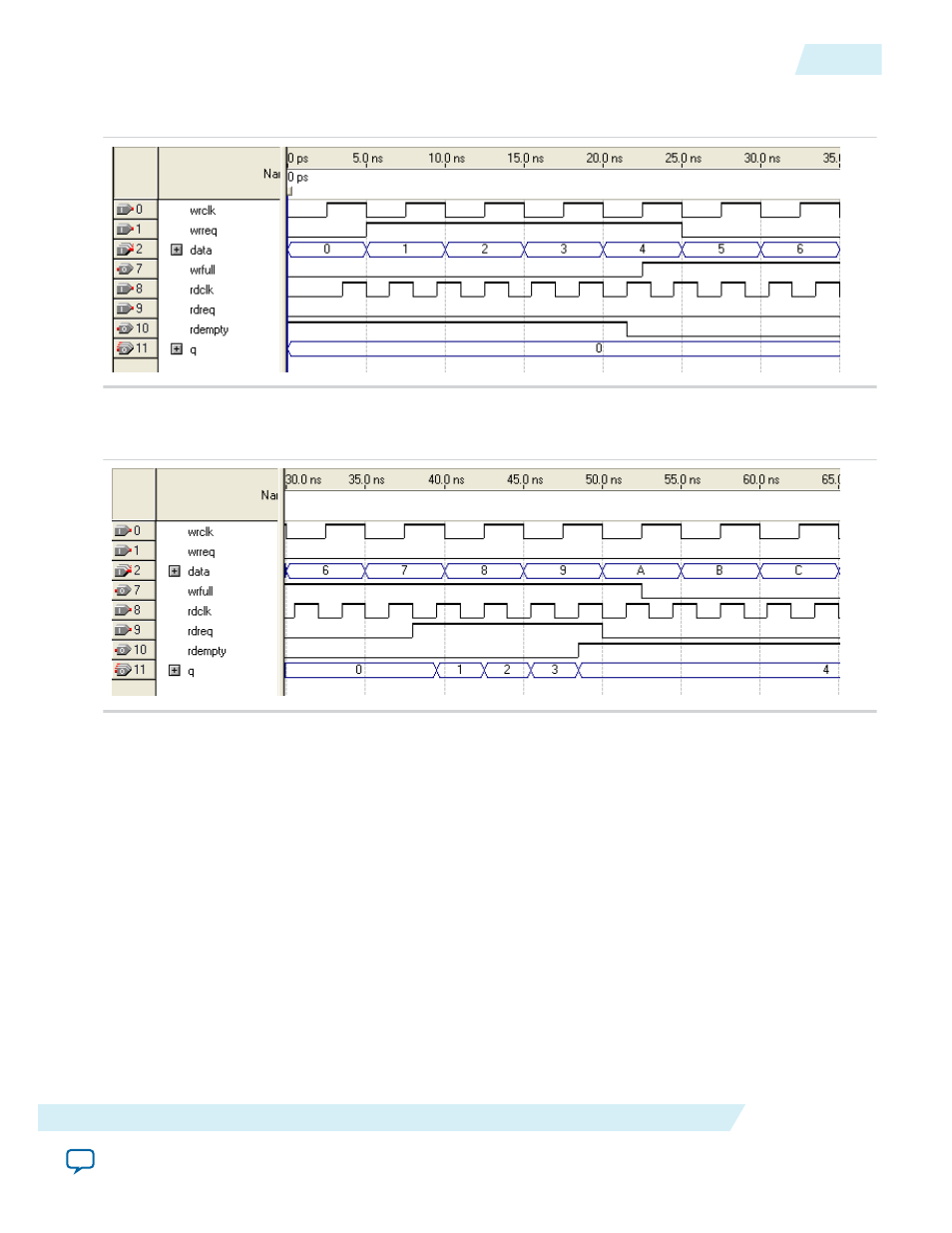

Figure 2: Functional Timing for the wrreq Signal and the wrfull Signal

This figure shows the behavior for the

wrreq

and the

wrfull

signals.

Figure 3: Functional Timing for the rdreq Signal and the rdempty Signal

This shows the behavior for the

rdreq

the

rdempty

signals.

The required functional timing for the DCFIFO as described previously is also applied to the SCFIFO.

The difference between the two modes is that for the SCFIFO, the

wrreq

signal must meet the functional

timing requirement based on the

full

signal and the

rdreq

signal must meet the functional timing

requirement based on the

empty

signal.

SCFIFO and DCFIFO Output Status Flag and Latency

The main concern in most FIFO design is the output latency of the read and write status signals.

UG-MFNALT_FIFO

2014.12.17

SCFIFO and DCFIFO Output Status Flag and Latency

11

SCFIFO and DCFIFO IP Cores User Guide

Altera Corporation