Altera SCFIFO User Manual

Page 24

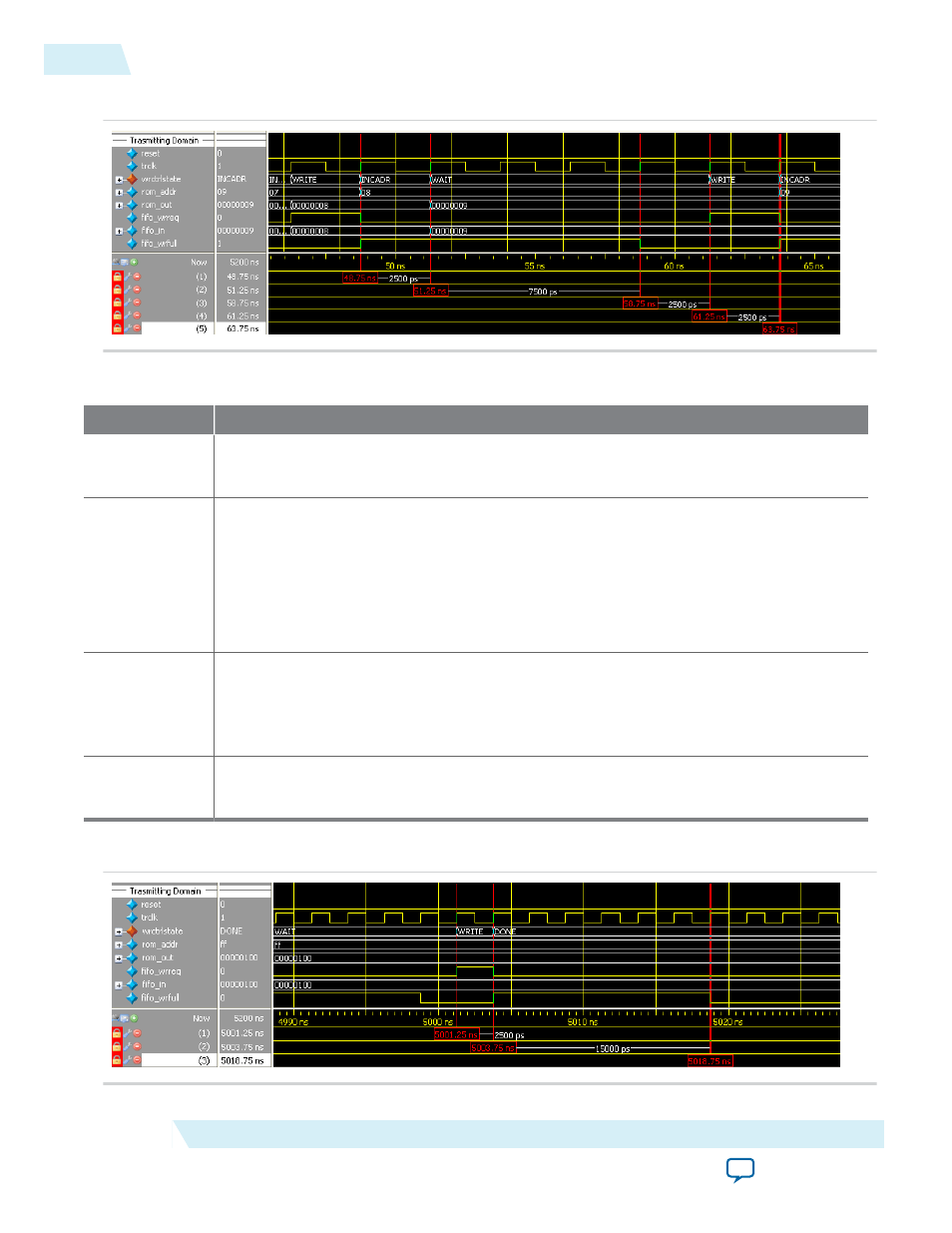

Figure 9: Write Operation when DCFIFO is FULL

Table 14: Write Operation when DCFIFO is FULL Waveform Description

State

Description

INCADR

When the write controller is in the

INCADR

state, and the

fifo_wrfull

signal is asserted,

the write controller transitions to the

WAIT

state in the next rising clock edge.

WAIT

In the

WAIT

state, the write controller holds the

rom_addr signal

(08) so that the

respective data is written into the DCFIFO when the write controller transitions to the

WRITE

state.

The write controller stays in

WAIT

state if the

fifo_wrfull

signal is still high. When the

fifo_wrfull

is low, the write controller always transitions from the

WAIT

state to the

WRITE

state at the next rising clock edge.

WRITE

In the

WRITE

state, then only the write controller drives the

fifo_wrreq

signal to high, and

requests for write operation to write the data from the previously held address (08) into

the DCFIFO. It always transitions to the

INCADR

state in the next rising clock edge, if the

rom_addr

signal has not yet increased to ff.

--

The same state transition continues as stated in

INCADR

,

WAIT

, and

WRITE

states, if the

fifo_wrfull

signal is high.

Figure 10: Completion of Data Transfer from ROM to DCFIFO

24

Design Example

UG-MFNALT_FIFO

2014.12.17

Altera Corporation

SCFIFO and DCFIFO IP Cores User Guide