Scfifo and dcfifo functional timing requirements – Altera SCFIFO User Manual

Page 10

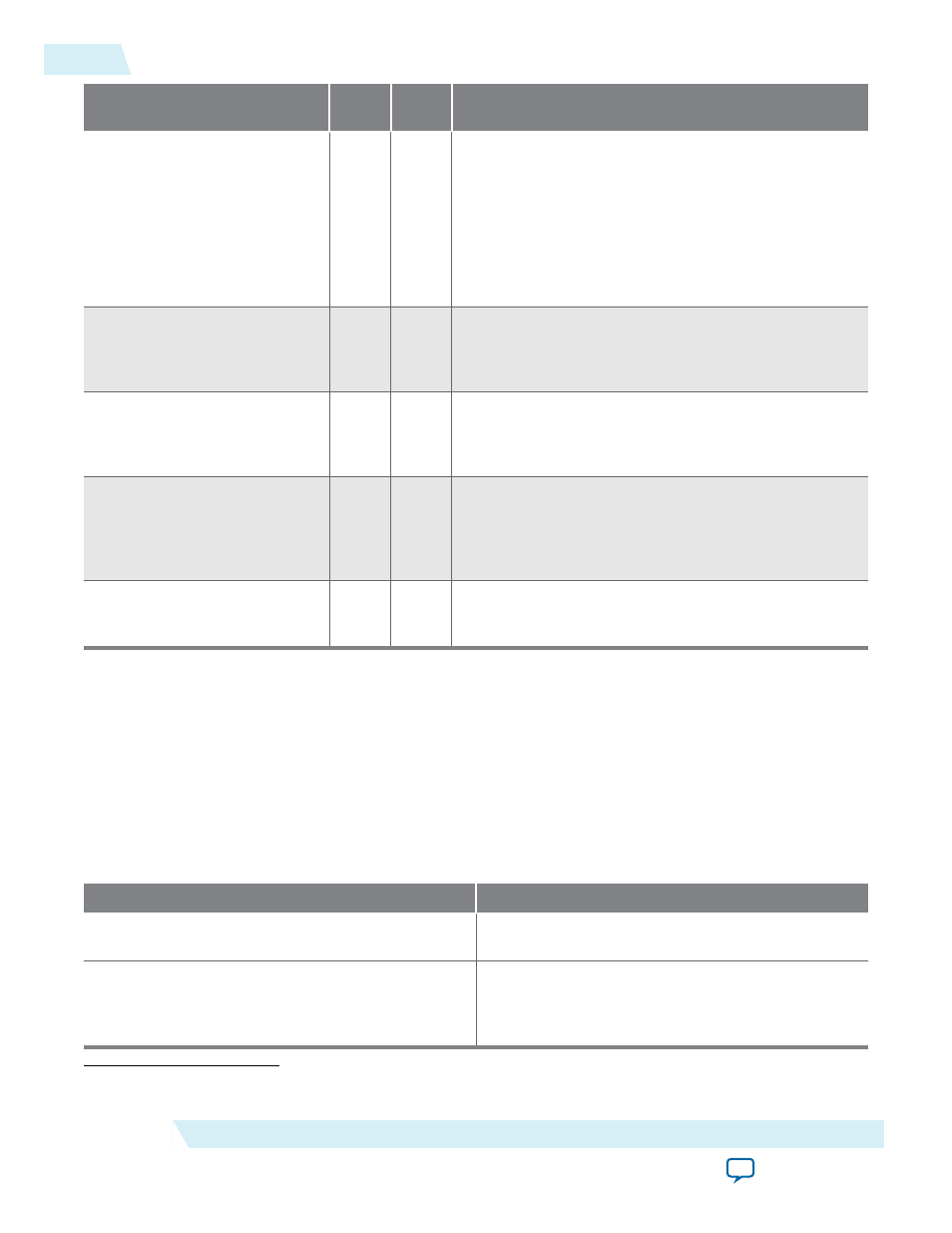

Parameter

Type

Requir

ed

Description

add_ram_output_register

String

No

Specifies whether to register the

q

output. The values

are ON and OFF. If omitted, the default value is OFF.

You can set the parameter to ON or OFF for the

SCFIFO or the DCFIFO, that do not target Stratix II,

Cyclone II, and new devices. This parameter does not

apply to these devices because the

q

output must be

registered in normal mode and unregistered in show-

ahead mode for the DCFIFO.

almost_full_value

Integer

No

Sets the threshold value for the

almost_full

port.

When the number of words stored in the FIFO IP core

is greater than or equal to this value, the

almost_full

port is asserted.

almost_empty_value

(6)

Integer

No

Sets the threshold value for the

almost_empty

port.

When the number of words stored in the FIFO IP core

is less than this value, the

almost_empty

port is

asserted.

allow_wrcycle_when_full

(6)

String

No

Allows you to combine read and write cycles to an

already full SCFIFO, so that it remains full. The values

are ON and OFF. If omitted, the default is

OFF

. Use

only this parameter when the

OVERFLOW_CHECKING

parameter is set to ON.

intended_device_family

String

No

Specifies the intended device that matches the device

set in your Quartus II project. Use only this parameter

for functional simulation.

SCFIFO and DCFIFO Functional Timing Requirements

The

wrreq

signal is ignored (when FIFO is full) if you enable the overflow protection circuitry in the FIFO

parameter editor, or set the

OVERFLOW_CHECKING

parameter to

ON

. The

rdreq

signal is ignored (when

FIFO is empty) if you enable the underflow protection circuitry in the FIFO MegaWizard interface, or set

the

UNDERFLOW_CHECKING

parameter to

ON

.

If the protection circuitry is not enabled, you must meet the following functional timing requirements:

Table 3: Functional Timing Requirements

DCFIFO

SCFIFO

Deassert the wrreq signal in the same clock cycle

when the

wrfull

signal is asserted.

Deassert the

wrreq

signal in the same clock cycle

when the

full

signal is asserted.

Deassert the

rdreq

signal in the same clock cycle

when the

rdempty

signal is asserted. You must

observe these requirements regardless of expected

behavior based on

wrclk

and

rdclk

frequencies.

Deassert the

rdreq

signal in the same clock cycle

when the

empty

signal is asserted.

(6)

Only applicable for the SCFIFO IP core.

10

SCFIFO and DCFIFO Functional Timing Requirements

UG-MFNALT_FIFO

2014.12.17

Altera Corporation

SCFIFO and DCFIFO IP Cores User Guide