Altera SCFIFO User Manual

Page 27

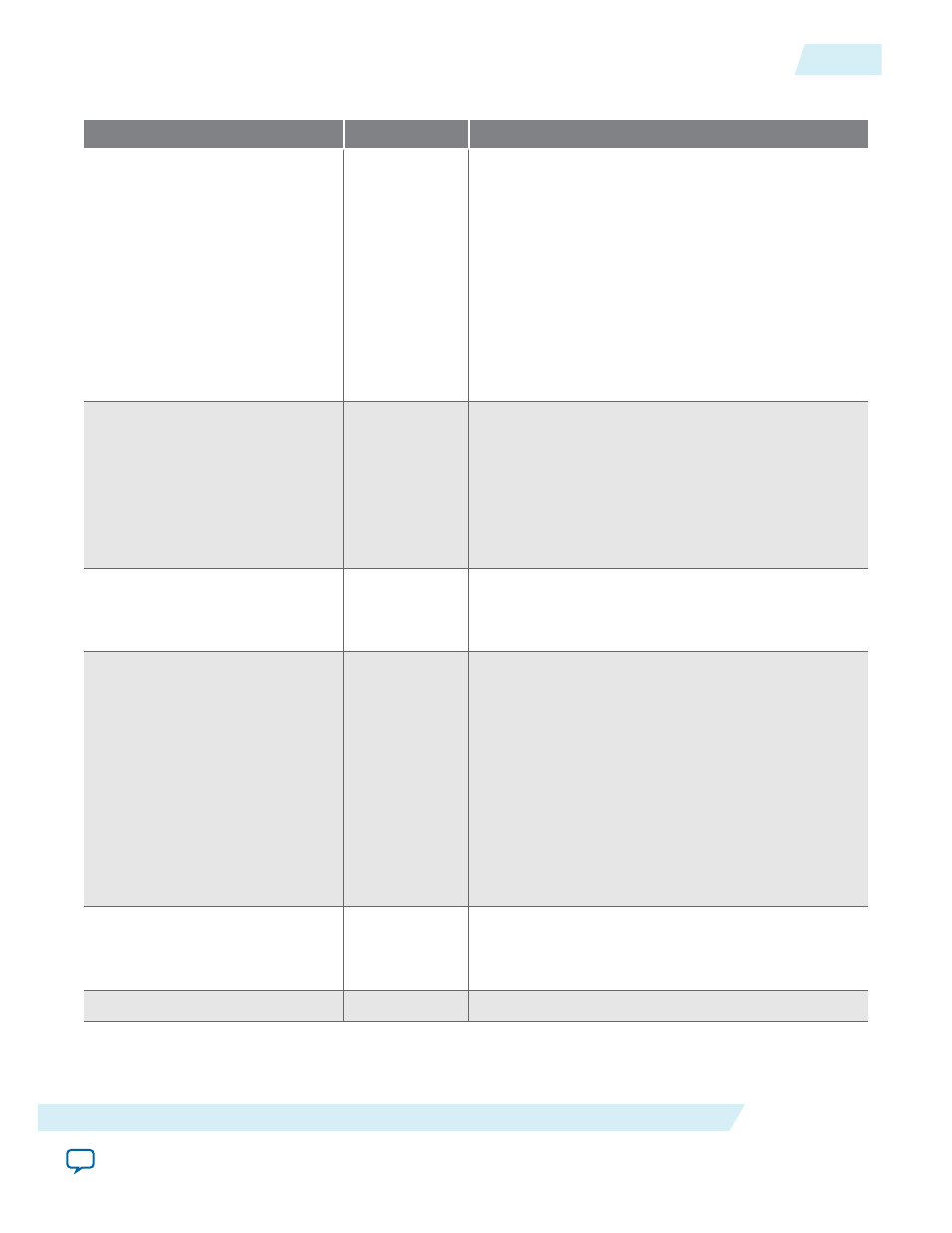

Table 16: Document Revision History

Date

Version

Changes

December 2014

2014.12.17

• Clarified that there are no minimum number of

clock cycles for

aclr

signals that must remain

active.

• Added Recovery and Removal Timing Violation

Warnings when Compiling a DCFIFO Megafunc‐

tion section.

• Removed a note about ignoring any recovery and

removal violation reported in the TimeQuest

timing analyzer that represent transfers from the

aclr to the read side clock domain in Synchronous

Clear and Asynchronous Clear Effect section.

May 2013

8.2

• Updated Table 8 on page 20 to state that both the

read and write pointers reset to zero upon

assertion of either the

sclr

or

aclr

signal.

• Updated Table 1 on page 7 to note that the

wrusedw

,

rdusedw

,

wrfull

,

rdfull wrempty

and

rdempty

values are subject to the latencies listed

in Table 5 on page 18.

August 2012

8.1

• Included a link to

skew_report.tcl

“Gray-Code

Counter Transfer at the Clock Domain Crossing”

on page 29.

August 2012

8.0

• Updated “DCFIFO” on page 3, “Ports Specifica‐

tions” on page 6, “Functional Timing Require‐

ments” on page 14, “Synchronous Clear and

Asynchronous Clear Effect” on page 20.

• Updated Table 1 on page 7, Table 2 on page 10,

Table 9 on page 21.

• Added Table 4 on page 16.

• Renamed and updated “DCFIFO Clock Domain

Crossing Timing Violation” to “Gray-Code

Counter Transfer at the Clock Domain Crossing”

on page 29.

February 2012

7.0

• Updated the notes for Table 4 on page 16.

• Added the “DCFIFO Clock Domain Crossing

Timing Violation” section.

September 2010

6.2

Added prototype and component declarations.

UG-MFNALT_FIFO

2014.12.17

Document Revision History

27

SCFIFO and DCFIFO IP Cores User Guide

Altera Corporation