Altera SCFIFO User Manual

Page 16

SCFIFO and DCFIFO Synchronous Clear and Asynchronous Clear Effect

The FIFO IP cores support the synchronous clear (

sclr

) and asynchronous clear (

aclr

) signals,

depending on the FIFO modes. The effects of these signals are varied for different FIFO configurations.

The SCFIFO supports both synchronous and asynchronous clear signals while the DCFIFO support

asynchronous clear signal and asynchronous clear signal that synchronized with the write and read clocks.

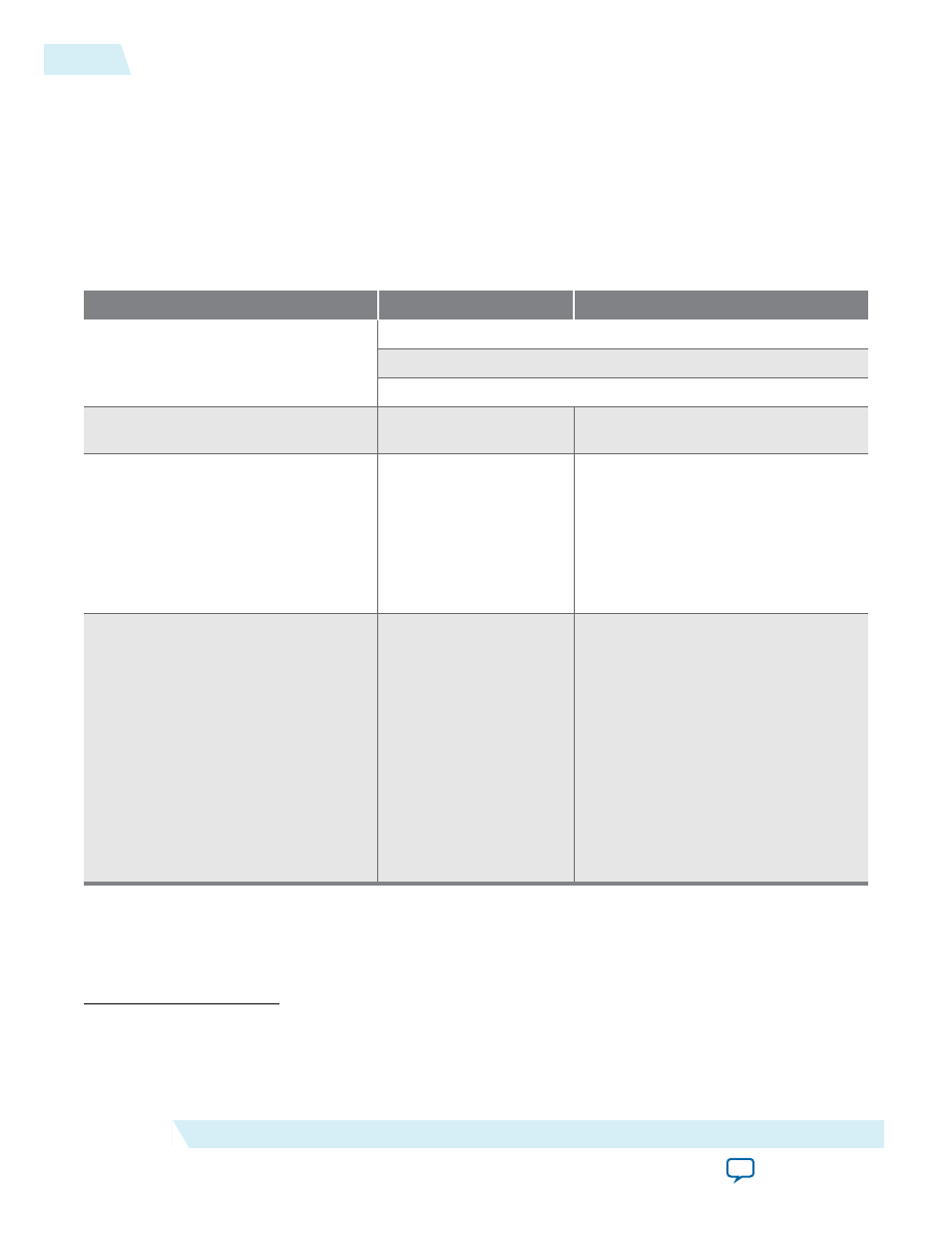

Table 9: Synchronous Clear and Asynchronous Clear in the SCFIFO

This table shows the synchronous clear and asynchronous clear signals supported in the SCFIFO.

Mode

Synchronous Clear (sclr)

(18)

Asynchronous Clear (aclr)

(18)

Effects on status ports

Deasserts the

full

and

almost_full

signals.

Asserts the

empty

and

almost_empty

signals.

Resets the

usedw

flag.

Commencement of effects upon

assertion

At the rising edge of the

clock.

Immediate (except for the

q

output)

Effects on the

q

output for normal

output modes

The read pointer is reset

and points to the first data

location. If the

q

output is

not registered, the output

shows the first data word

of the SCFIFO; otherwise,

the

q

output remains at its

previous value.

The

q

output remains at its previous

value.

Effects on the

q

output for show-

ahead output modes

The read pointer is reset

and points to the first data

location. If the

q

output is

not registered, the output

remains at its previous

value for only one clock

cycle and shows the first

data word of the SCFIFO

at the next rising clock

edge.

(19)

Otherwise, the

q

output

remains at its previous

value.

If the

q

output is not registered, the

output shows the first data word of

the SCFIFO starting at the first rising

clock edge.

(19)

Otherwise, the

q

output remains its

previous value.

(18)

The read and write pointers reset to zero upon assertion of either the

sclr

or

aclr

signal.

(19)

The first data word shown after the reset is not a valid Show-ahead data. It reflects the data where the read

pointer is pointing to because the

q

output is not registered. To obtain a valid Show-ahead data, perform a

valid write after the reset.

16

SCFIFO and DCFIFO Synchronous Clear and Asynchronous Clear Effect

UG-MFNALT_FIFO

2014.12.17

Altera Corporation

SCFIFO and DCFIFO IP Cores User Guide