Pi632&pi672, Chapt.2 specifications, Sequence controller s2t – Toshiba SX 2000 User Manual

Page 123

Attention! The text in this document has been recognized automatically. To view the original document, you can use the "Original mode".

Chapt.2 Specifications

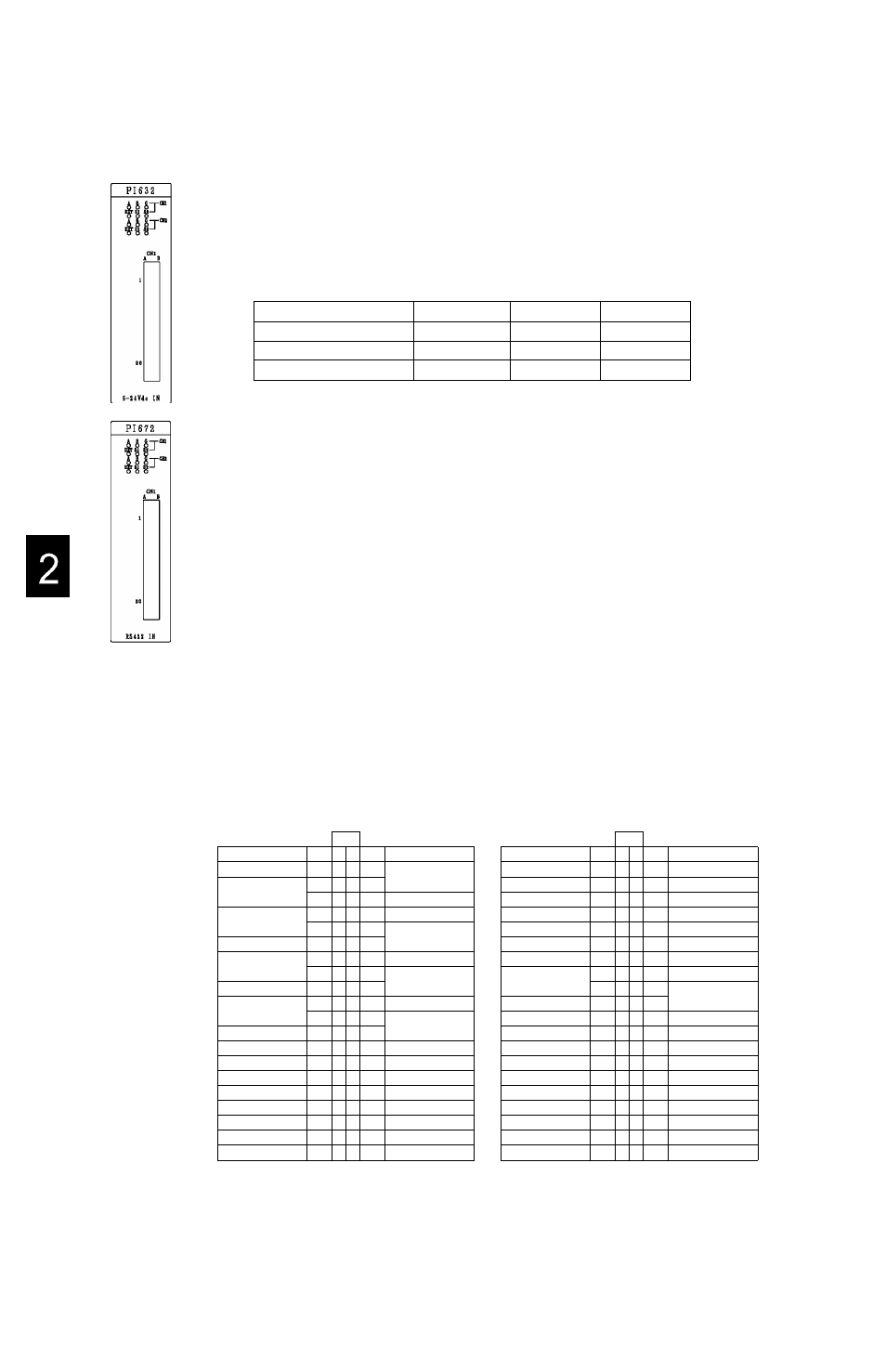

PI632&PI672

Item

No. of pulse input channel

I/O allocation type

Input Voltage Range (A,B,M)

Input Voltage Range (G,EXT)

Input

Spec.

(A,B,

M,G)

Input Voltage

5Vdc

12Vdc

24Vdc

Input current (typ.)

13mA

15mA

16mA

Minimum ON Voltage

3.75V or more

9.5V or more

21V or more

Maximum OFF Voltage

1.25V or less

2.5V or less

5V or less

Input

Spec.

(EXT)

Input Voltage

Input current (typ.)

Minimum ON Voltage

Maximum OFF Voltage

Pulse duration

(ON/OFF level)

ON/OFF transition

Counter configuration

Input pulse frequency

Pulse count mode

Flardware comparison output

function

Output

Spec.

Output Voltage

Output current

Withstand voltage

Current consumption

Weight

PI632

2 channels

PI672

2 channels

X+YW 4W area (input/output inhibit) and 19W memory

5V±5% /12V±5% /24V±5%

(selectable)

Conforms to EIA RS-422-A

12V±5% /24V±5%

RS422

EIA standard

RS-422-A

Am26LS31

12V/24Vdc

10mA

9.6V or more

3.5V or less

Sms or more (other than quadrature bi-pulse)

10ms or more (quadrature bi-pulse)

1.5ms or less (other than quadrature bi-pulse)

3ms or less (quadrature bi-pulse)

24-bit, binary counter, Count value=0 to 16777215)

lOOkpps maximum (other than quadrature bi-pulse)

SOkpps maximum (quadrature bi-pulse)

Normal mode (1 count per 1 pulse)

Precision count mode (both rising and falling edges)

2 points for each channel (transistor output)

*S1: ON when Count value > set-point 1

*S2: ON when Count value < set-point 2

24Vdc (10Vdc~30Vdc)

100mA or less

1500Vac/1 minute

500mA(5Vdc) or less

Approx. 250g

500Vac /1 minute

650mA(5Vdc) or less

Approx. 250g

Connector Assignment

PI632

PI672

Rn No.

Fm ctio i

Nane

A

B

Nane

Fin cücn

Q Tanel 1 RiaseAirpjt

1A5

1

1

1AP

Q raral 1 FtaseAirput

Q Tanel 1 RiaseBirpjt

1BP

2

2

1A12

1B12

3

3

1B5

Q raral 1 Ftase B irput

Q Tanel 1 !\/H 1M P 4 4 IM S Q raral 1 W y 1M 12 5 5 24P Q raral 2 Ftase A irpjt Q Tanel 2 Rase A irpjt 2A5 6 6 2A12 Q Tanel 2 Rase B irpjt 2BP 7 7 2B5 Q raral 2 Ftase B irput 2B12 8 8 2№ Q raral 2 W y Q Taral 2 !\/H 2M 5 9 9 2M 12 Q Taral 1 G ate irpjt 1G P 10 10 1G 5 Q raral 1 CM ei^xit 1G 12 11 11 2G P Q raral 2 CM e i^xit Q Taral 2 G ate irpjt 2G 5 12 12 2G 12 Channel 1 External lim it input 1E)Cr- 13 13 IBCT-f- Channel 1 External lim it input Channel 2 External lim it input 2EXT- 14 14 2E)Cr-f- Channel 2 External lim it input Channel 1 Com pare output 2 1^ 15 15 1S1 Channel 1 Com pare output 1 Channel 2 Com pare output 2 2^ 16 16 2S1 Channel 2 Com pare output 1 No use 17 17 No use 24Vdcirpjt P24 18 18 P24 24VdcirpU 0 V fcr anpae oitxits N24 19 19 N24 0 V for ccnpae oitxits No use 20 20 No use Rn No. Furcticn Nane A B Nane Firaticxr Q raral 1 FtaseA^- lAi- 1 1 1A- Q raral 1 FtaseA- Q iarall FtaseBi- IB-H 2 2 IB- Q raral 1 FtaseB- Q raral 1 wy IM -H 3 3 1M - Q raral 1 wy Q raral 2 Ftase A 2Ai- 4 4 2A- Q raral 2 Ftase A- Q raral 2 Ftase B 2Bi- 5 5 2B- Q raral 2 FtaseB- Q raral 2 W y 2M i- 6 6 2M - Q raral 2 W y Line receiver sigid gojid SG 7 7 SG Lira receiver sigid gojid Q raral 1 CM ei^xit 1G 24 8 8 1G 12 Q raral 1 CM ei^xit 1G P 9 9 2G P Q raral 2 G ate irput Q raral 2 CM e i^xit 2G 12 10 10 2G 24 No use 11 11 No use Channel 1 External lim it input IBCT- 12 12 lEXT-f- Channel 1 External lim it input Channel 2 External lim it input 2EXT- 13 13 2EXT-f- Channel 2 External lim it input No use 14 14 No use Channel 1 Com pare output 2 1^ 15 15 1S1 Channel 1 Com pare output 1 Channel 2 Com pare output 2 2^ 16 16 2S1 Channel 2 Com pare output 1 No use 17 17 No use 24Vdcirput P24 18 18 P24 24VdcirpU 0 V for ccnpaa oitxits N24 19 19 N24 0 V fcr anpaa oitxits No use 20 20 No use 1 0 6 Sequence Controller S2T