Kontron COMe-cPV2(v1.4) User Manual

Page 45

Kontron microETXexpress-PV User’s Guide

41

it can be used as an external super I/O controller to combine legacy-device

support into a single IC. The implementation of this subsystem complies with

the COM Express® specification. For additional implementation information,

refer to the PICMG COM Express® Design Guide on the PICMG website.

The LPC bus does not support DMA (Direct Memory Access) and therefore imposes

limitations for ISA bus and standard I/Os (SIOs) like floppy or LPT interface

implementations.

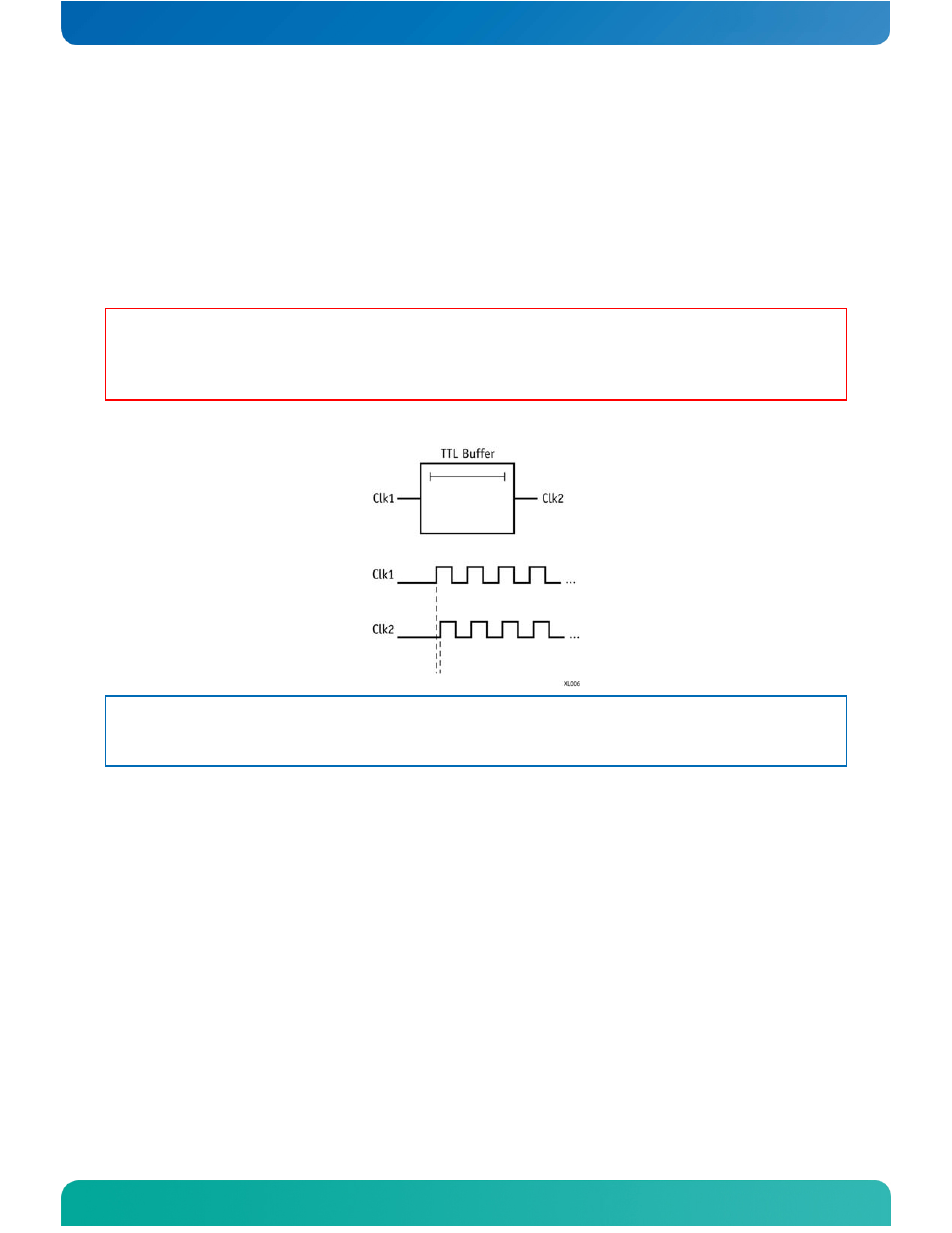

WARNING:

Connecting more than one device to the LPC bus requires using a

clock buffer. Because of the power management of the LPC bus, you

must use great care with clock buffers that require synchronization

as they could prevent the board from booting up.

Figure 6: Standard Clock Buffer

NOTE: When using a standard clock buffer on the baseboard, be aware that the

generated delay must be considered for the length matching of the

layout.

Clock Buffer Reference Schematic

The schematic in Figure 7 shows an implementation example for the clock

buffer.

Figure 7: LPC Clock Buffer