Kontron VM162 User Manual

Page 39

VM162/VM172

Chapter 2 Functional Description

Juli 23, 1997

Page 2- 17

© PEP Modular Computers

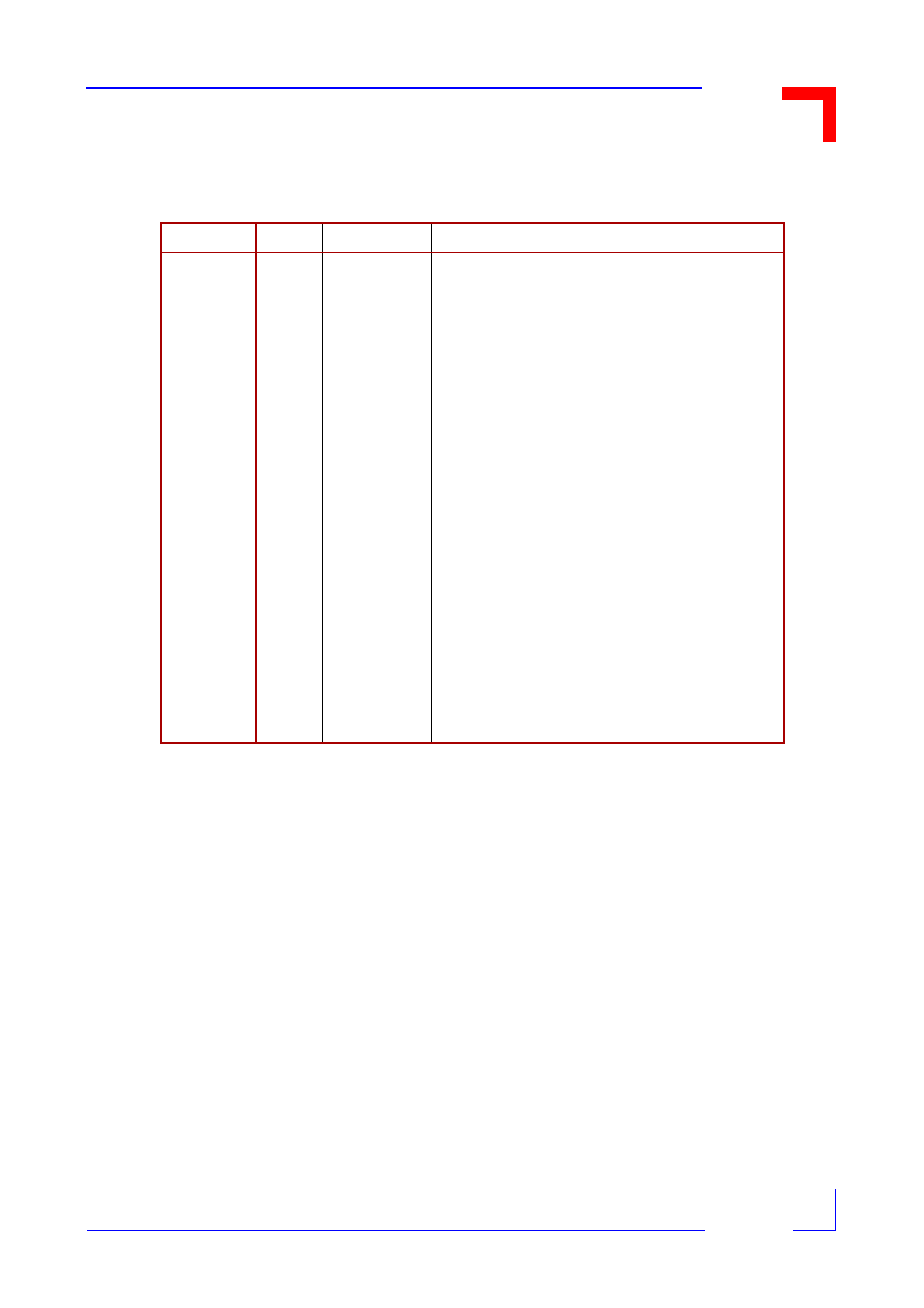

Register Description

Name

Value

Access

Description

WDG

bit 7

BERR2

bit 6

BERR1

bit 5

EN_WDG

bit 4

TR_WDG

bit 3

EN_BERR1

bit 2

ACFAIL

bit 1

LED_G

bit 0

1

1

1

1

1

Read/Write

Read/Write

Read/Write

Read/Write

Read/Write

Read/Write

Read/Write

Read/Write

Set by watchdog timer when timeout has been reached.

Used to differentiate between resets caused by the

watchdog and resets caused by the reset button (power up

resets can be identified within the 68EN360).

Set by VMEbus BUS monitor when timeout has been

reached. Used to identify BERR caused by this timer (see

also VMEbus Control/Status Register).

Set by on-board bus error timer when timeout has been

reached. Used to identify BERR caused by this timer.

Enable the watchdog timer. It can only be set once, and

remains enabled until the next reset.

Triggers the watchdog timer. Watchdog timeout=512ms.

Enables the on-board bus error timer. It also monitors all

on-board I/O cycles, including the time from the VMEbus

request to the VMEbus grant. Timeout=8

µ

s.

VME ACFAIL signal latched when active in order to

distinguish between a level 7 NMI from an ABORT or

ACFAIL.

Enables the green ‘general purpose’ front panel LED.