5 vme control/status register, Vme control/status register -13 – Kontron VM162 User Manual

Page 35

VM162/VM172

Chapter 2 Functional Description

Juli 23, 1997

Page 2- 13

© PEP Modular Computers

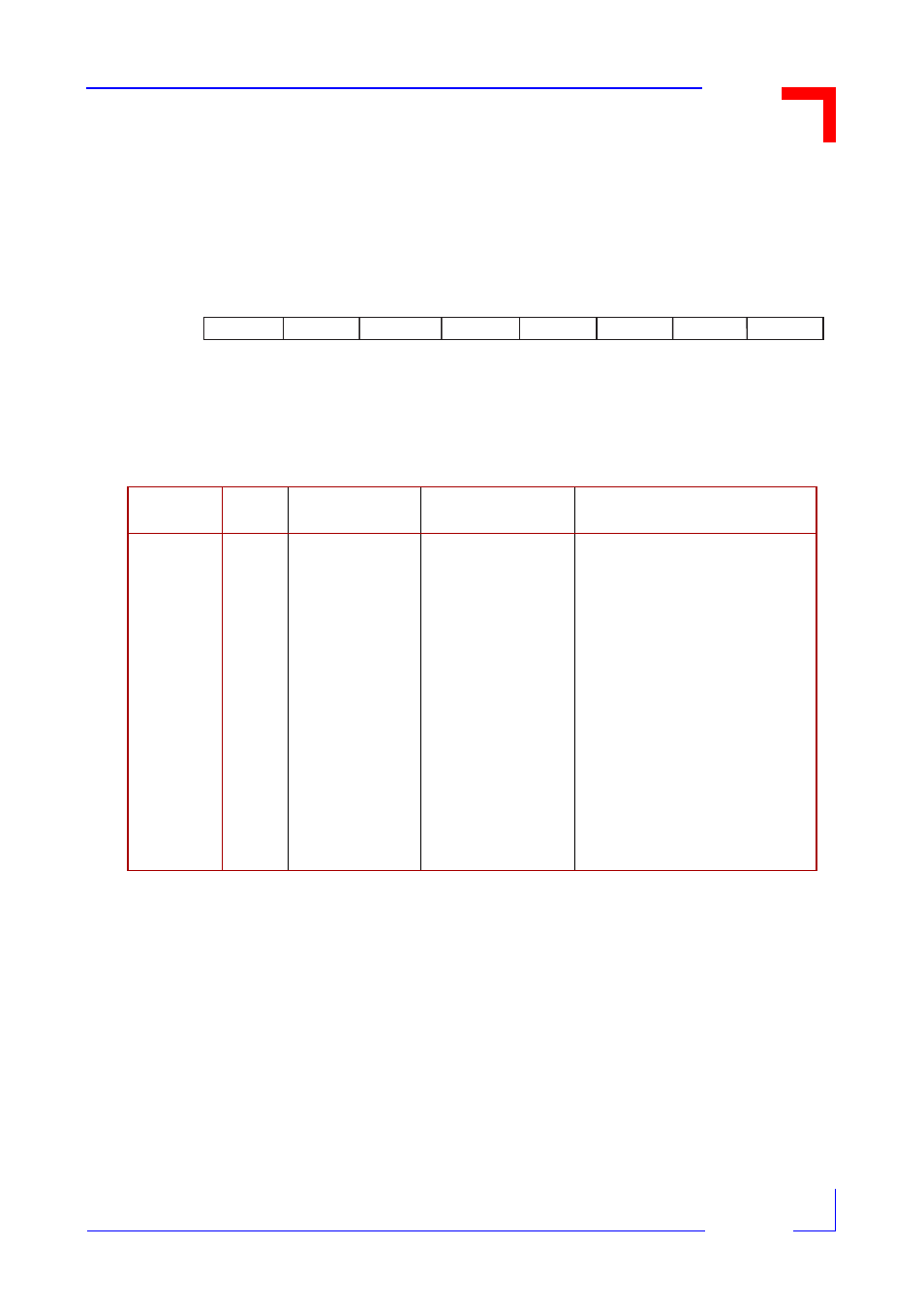

2.5.5 VME Control/Status Register

The VME Control/Status Register is a one byte wide register with read/write access at default address

CD 00 00 05 (HEX).

Note: All bits except bit 4 (First Slot Detection) are cleared after reset. The firmware of the board initia-

lizes some of them at startup according to the default parameters stored in the EEPROM.

Register Description

Note: All bits are cleared during a reset. FSD is set dependent on the slot position of the board in the

system. The board’s firmware initializes EN_DTR, EN_BERR2 and BADR[3-0] during startup follo-

wing default parameters stored in the serial EEPROM.

Name

Value

Reset (HW)

Slot 1

Other

Reset PEP (SW)

Slot 1

Other

Description

P_IRQ5

bit 7

EN_DPR

bit 6

EN_BERR2

bit 5

FSD

bit 4

BADR3 -

BADR0

bits 3-0

1

1

1

1

0

0

0

0

0

0

1

0

0

0

0

0

Value stored in

EEPROM

1

0

1

0

Value stored in

EEPROM

Pending mailbox IRQ

Dual-port RAM (inc. mailbox IRQ) for

VME requester enabled. Base address

fixed using BADRx bits

Enable bus monitor timer, all VME

cycles, timeout after 128

µ

s

VMEbus ‘First Slot Detection’ flag,

system controller

VME address location of dual-ported

RAM. Equivalent to VME address lines

A23-A20, programmable from $0-$F in

1 MByte windows, enabled with

EN_DPR

BADR2

BADR3

BADR1

BADR0

CS7 + $5

0

1

2

3

4

5

6

7

P_IRQ5

FSD

EN_BERR2

EN_DPR