Rockwell Automation 1771-N SERIES High Resolution Analog Module User Manual User Manual

Page 79

7–3

Troubleshooting

Publication 1771ĆUM127B-EN-P - December 2002

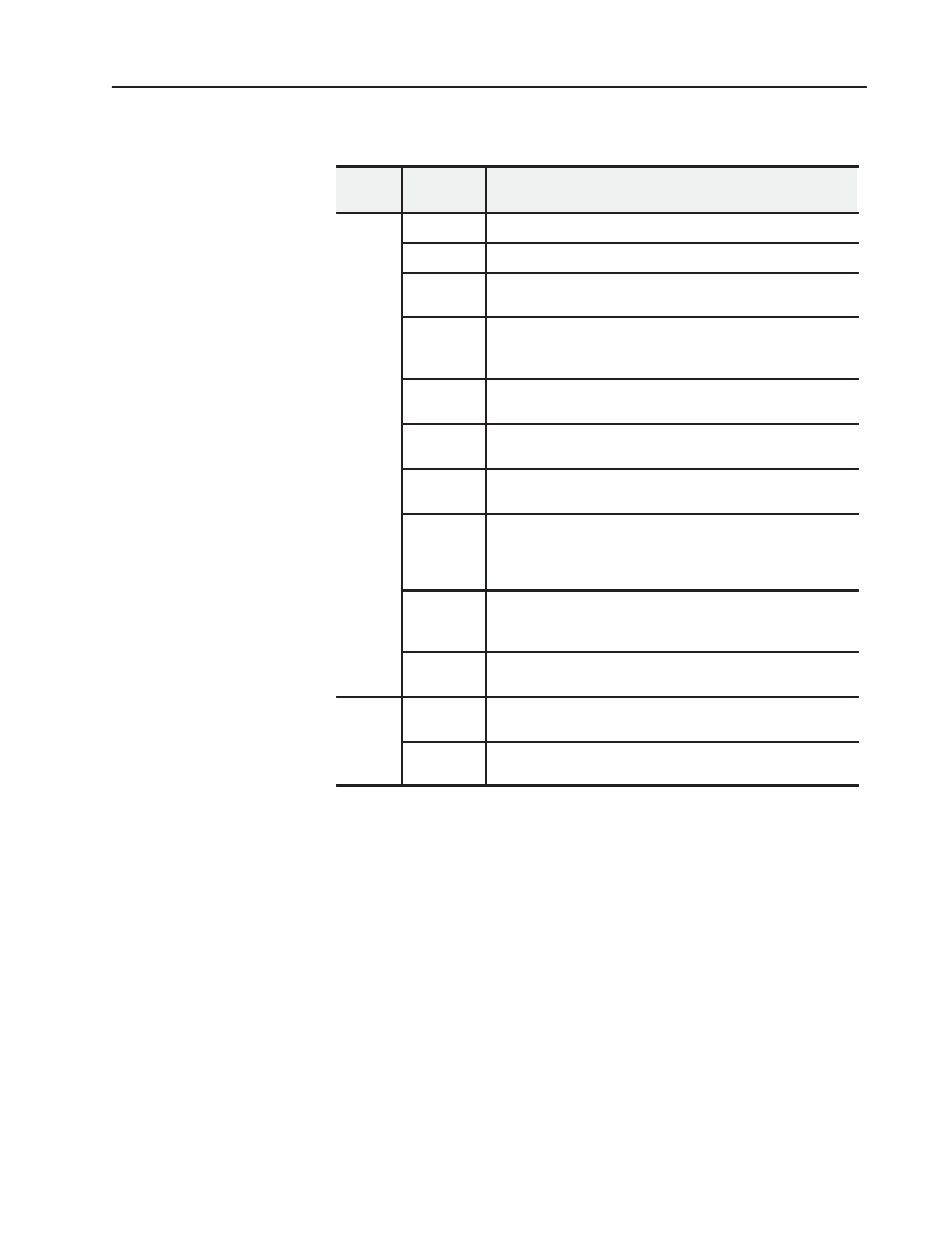

Table 7.B

Module Status Reported in BTR Word 1

Decimal Bit

(Octal Bit)

Explanation

Word 1

Bit 00Ć05

Not used

Bit 06

Bad structure. This bit is set if there is an error in the BTW header.

Bit 07

Bad program. This bit is set if any of the module level programming

data is illegal.

Bit 08 (10)

Module fault. This bit is set if any of the programming data sent to the

module in the most recent BTW was illegal, or if one or more channels

has the bad calibration bit set.

Bits 09Ć10

(11Ć12)

Program verify. Indicates the result of verify request. 00 = verify not

requested; 10 = verify failed; 11 = verify succeeded

Bit 11 (13)

I/O reset. This bit is set whenever the I/O reset line on the backplane

is asserted.

Bit 12 (14)

RTS timeout. This bit is set if no BTR was requested of the module

within the RTS sample time.

Bit 13 (15)

Module alarm. This bit is set if there is an alarm bit set for one or more

channels. The input alarm bits are low, high alarm and rate alarm. The

output channel alarm bits are low and high clamp, and the rate limit

alarm.

Bit 14 (16)

Bad channel data. This bit is set if the module is in BCD mode and

one or more of the input data values sent in the last BTW are not a

legal BCD value.

Bit 15 (17)

Powerup bit. This bit is set until a BTW with programming data is

received by the module.

Word 2

Bit 00

CJC Underrange bit. This bit is set if the CJC temperature is below the

input channel minimum range.

Bit 01

CJC Overrange bit. This bit is set if the CJC temperature is above the

input channel maximum range.