Figure 9-26, Multiword dma data transfer timing diagram – AMD Geode SC3200 User Manual

Page 388

388

AMD Geode™ SC3200 Processor Data Book

Electrical Specifications

32581C

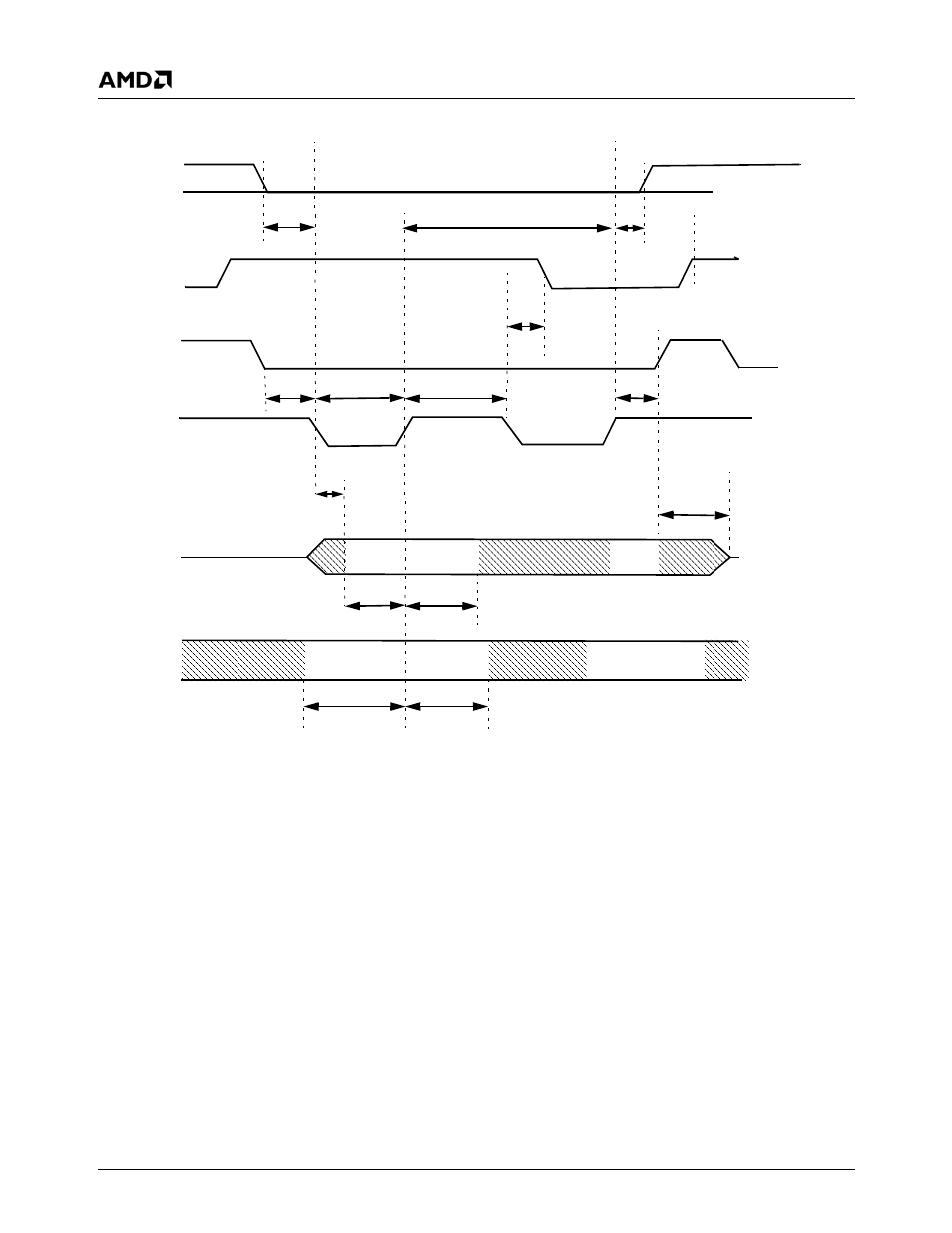

Figure 9-26. Multiword DMA Data Transfer Timing Diagram

t

M

t

N

t

L

t

j

t

K

t

D

t

I

t

E

t

Z

t

F

t

G

t

G

t

H

t

0

IDE_CS[1:0]#

IDE_DATA[15:0]

IDE_DATA[15:0]

IDE_DREQ0

IDE_DACK0#

IDE_IOR0#

IDE_IOW0#

Notes:

1)

For Multiword DMA transfers, the Device may negate IDE_DREQ[0:1] within the tL specified time once IDE_DACK[0:1

is asserted, and reassert it again at a later time to resume the DMA operation. Alternatively, if the device is able to co

tinue the transfer of data, the device may leave IDE_DREQ[0:1] asserted and wait for the host to reasse

IDE_DACK[0:1]#.

2)

This signal can be negated by the host to Suspend the DMA transfer in process.

See also other documents in the category AMD Hardware:

- Radeon 4850 (18 pages)

- Phenom AM2r2 (6 pages)

- GA-K8N51GMF-9 (80 pages)

- Socket AM2+ Quad Core Processor SB750 (63 pages)

- Turion 64 X2 (2 pages)

- GA-M61PM-S2 (80 pages)

- Socket AM2+ Quad Core AMD Processor 790GX (53 pages)

- 7ZMMC (36 pages)

- Geode SC1200 (443 pages)

- CS5535 (36 pages)

- Geode LX800 (46 pages)

- ATI RADEON HD 2600 (62 pages)

- LE-363 (45 pages)

- SimNow Simulator 4.4.4 (269 pages)

- GA-MA69VM-S2 (88 pages)

- KM780V (21 pages)

- SBX-5363 (55 pages)

- AM79C971 (1 page)

- K3780E-S (43 pages)

- GEODE LE-366 (45 pages)

- 7ZX-1 (46 pages)

- Geode SC2200 (429 pages)

- Phenom II (6 pages)

- ATI Radeon x1700 FSC (22 pages)

- Turion 64 (3 pages)

- 1207 (62 pages)

- CrossFire 550X (16 pages)

- Athlon 27488 (104 pages)

- Geode LX [email protected] (680 pages)

- GA-M61SME-S2 (80 pages)

- N2PA-LITE (45 pages)

- GA-K8NSC-939 (80 pages)

- GEODE NX800LX (27 pages)

- Am79C930 (161 pages)

- LV-651 (50 pages)

- Athlon 6 (19 pages)

- SEMPRON 10 (102 pages)

- GA-K8N ULTRA-9 (80 pages)

- Geode LX CS5536 (8 pages)

- MINI-ITX LV-651 (50 pages)

- GA-K8N51GMF-RH (88 pages)

- ATI RADEON HD 2400 (64 pages)

- GA-M55S-S3 (88 pages)

- GA-M51GM-S2G (88 pages)