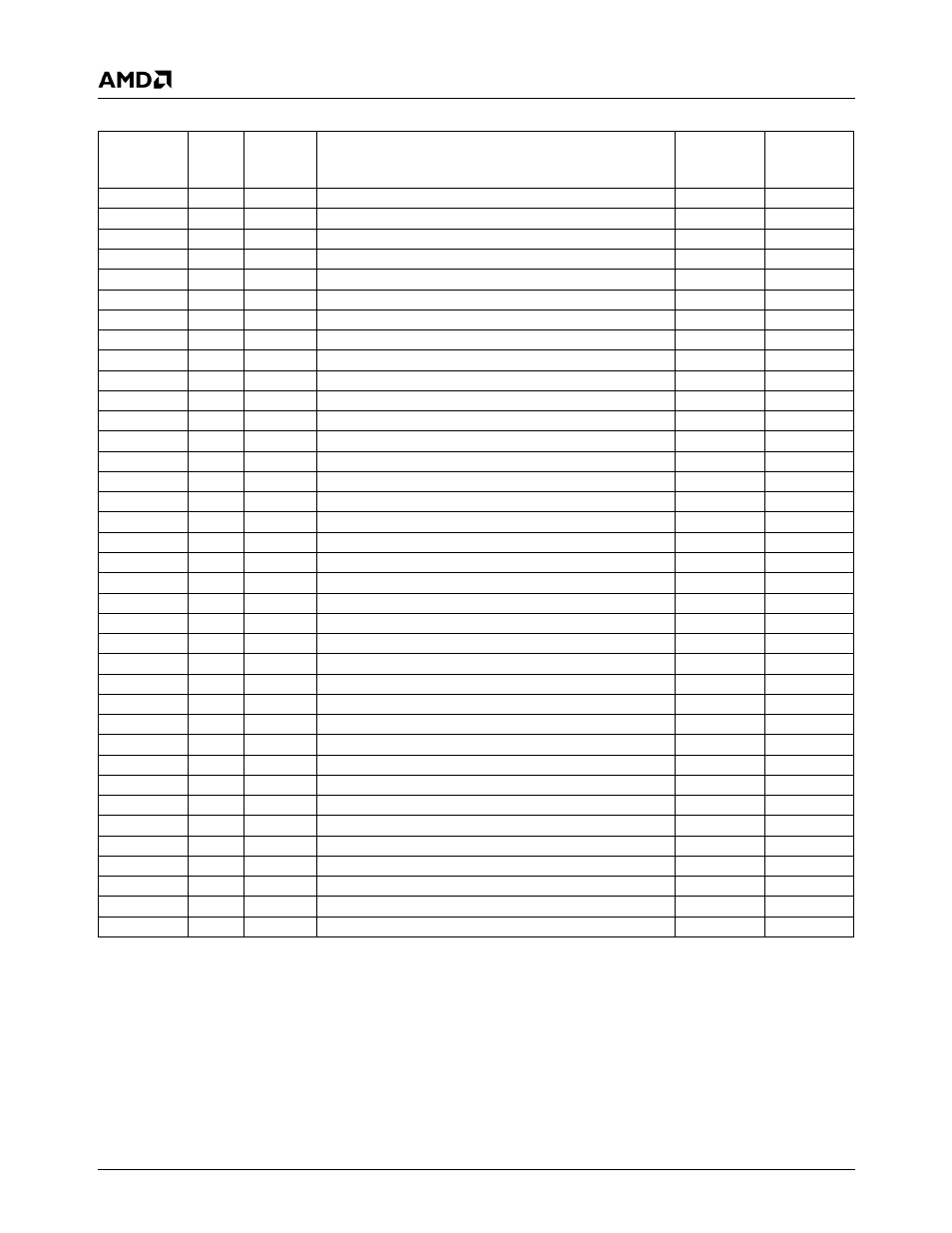

AMD Geode SC3200 User Manual

Page 328

328

AMD Geode™ SC3200 Processor Data Book

Video Processor Module - Register Summary

32581C

28h-2Bh

32

R/W

Miscellaneous Register

00001400h

Page 336

2Ch-2Fh

32

R/W

PLL2 Clock Select Register

00000000h

Page 336

30h-33h

32

---

Reserved

00000000h

Page 336

34h-37h

32

RO

Reserved

00000000h

Page 336

38h-3Bh

32

RO

Reserved

00000000h

Page 336

3Ch-3Fh

32

R/W

Video Downscaler Control Register

00000000h

Page 337

40h-43h

32

R/W

Video Downscaler Coefficient Register

00000000h

Page 337

44h-47h

32

R/W

CRC Signature Register

xxxxx100h

Page 337

48h-4Bh

32

RO

Device and Revision Identification

0000015xh

Page 337

4Ch-4Fh

32

R/W

Video De-Interlacing and Alpha Control Register

00060000h

Page 338

50h-53h

32

R/W

Cursor Color Key Register

00000000h

Page 339

54h-57h

32

R/W

Cursor Color Mask Register

00000000h

Page 339

58h-5Bh

32

R/W

Cursor Color Register 1

00000000h

Page 339

5Ch-5Fh

32

R/W

Cursor Color Register 2

00000000h

Page 339

60h-63h

32

R/W

Alpha Window 1 X Position Register

00000000h

Page 340

64h-67h

32

R/W

Alpha Window 1 Y Position Register

00000000h

Page 340

68h-6Bh

32

R/W

Alpha Window 1 Color Register

00000000h

Page 340

6Ch-6Fh

32

R/W

Alpha Window 1 Control Register

00000000h

Page 340

70h-73h

32

R/W

Alpha Window 2 X Position Register

00000000h

Page 341

74h-77h

32

R/W

Alpha Window 2 Y Position Register

00000000h

Page 341

78h-7Bh

32

R/W

Alpha Window 2 Color Register

00000000h

Page 341

7Ch-7Fh

32

R/W

Alpha Window 2 Control Register

00000000h

Page 341

80h-83h

32

R/W

Alpha Window 3 X Position Register

00000000h

Page 342

84h-87h

32

R/W

Alpha Window 3 Y Position Register

00000000h

Page 342

88h-8Bh

32

R/W

Alpha Window 3 Color Register

00000000h

Page 342

8Ch-8Fh

32

R/W

Alpha Window 3 Control Register

00000000h

Page 342

90h-93h

32

R/W

Video Request Register

001B0017h

Page 343

94h-97h

32

RO

Alpha Watch Register

00000000h

Page 343

98h-3FFh

---

Reserved

---

Page 343

400h-403h

32

R/W

Video Processor Display Mode Register

00000000h

Page 343

404h-407h

32

---

Reserved

00000000h

Page 343

408h-40Bh

32

R/W

Video Processor Test Mode Register

00000000h

Page 343

40Ch-41Fh

---

---

Reserved

00000000h

Page 343

420h-423h

32

R/W

GenLock Register

00000000h

Page 344

424h-427h

32

R/W

GenLock Delay Register

00000000h

Page 344

428h-43Bh

---

---

Reserved

---

Page 344

43Ch-43Fh

32

R/W

Continuous GenLock Time-out Register

1FFF1FFFh

Page 344

Table 7-4. F4BAR0: Video Processor Configuration Registers Summary (Continued)

F4BAR0+

Memory

Offset

Width

(Bits)

Type

Name

Reset

Value

Reference

(Table 7-7)