AMD Geode SC3200 User Manual

Page 240

240

AMD Geode™ SC3200 Processor Data Book

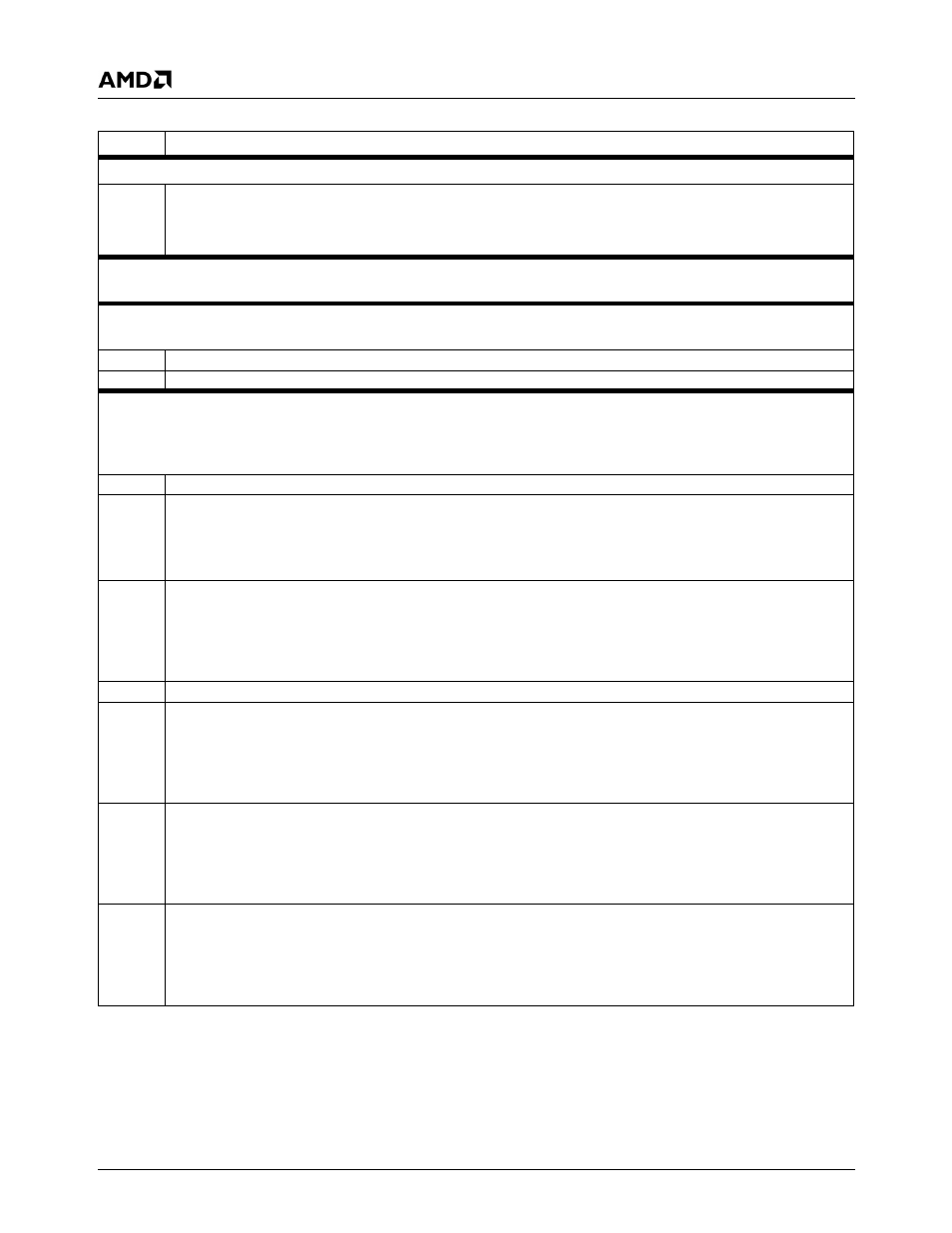

Core Logic Module - SMI Status and ACPI Registers - Function 1

32581C

Offset 08h-09h

SMI Speedup Disable Register (Read to Enable)

Reset Value: 0000h

15:0

SMI Speedup Disable. If bit 1 in the Suspend Configuration Register is set (F0 Index 96h[1] = 1), a read of this register

invokes the SMI handler to re-enable Suspend Modulation.

The data read from this register can be ignored. If the Suspend Modulation feature is disabled, reading this I/O location has

no effect.

Offset 0Ah-1Bh

Reserved

Reset Value: 00h

These addresses should not be written.

Offset 1Ch-1Fh

ACPI Timer Register (RO)

Reset Value: xxxxxxxxh

Note:

This register can also be read at F1BAR1+I/O Offset 1Ch.

31:24

Reserved.

23:0

TMR_VAL. This field returns the running count of the power management timer.

Offset 20h-21h

Second Level ACPI PME/SMI

Reset Value: 0000h

Status Mirror Register (RO)

The bits in this register contain second level SMI status reporting. Top level status is reported in F1BAR0+I/O Offset 00h/02h[2].

Reading this register does not clear the SMI. For more information, see F1BAR0+I/O Offset 22h.

15:6

Reserved. Always reads 0.

5

ACPI BIOS SMI Status. Indicates whether or not an SMI was caused by ACPI software raising an event to BIOS software.

0: No.

1: Yes.

To enable SMI generation, set F1BAR1+I/O Offset 0Ch[2] to 1, and F1BAR1+I/O Offset 0Fh[0] to 1.

4

PLVL3 SMI Status. Indicates whether or not an SMI was caused by a read of the ACPI PLVL3 register (F1BAR1+I/O Offset

05h).

0: No.

1: Yes.

To enable SMI generation, set F1BAR1+I/O Offset 18h[11] to 1 (default).

3

Reserved.

2

SLP_EN SMI Status. Indicates whether or not an SMI was caused by a write of 1 to the ACPI SLP_EN bit (F1BAR1+I/O

Offset 0Ch[13]).

0: No.

1: Yes.

To enable SMI generation, set F1BAR1+I/O Offset 18h[9] to 1 (default).

1

THT_EN SMI Status. Indicates whether or not an SMI was caused by a write of 1 to the ACPI THT_EN bit (F1BAR1+I/O

Offset 00h[4]).

0: No.

1: Yes.

To enable SMI generation, set F1BAR1+I/O Offset 18h[8] to 1 (default).

0

SMI_CMD SMI Status. Indicates whether or not an SMI was caused by a write to the ACPI SMI_CMD register (F1BAR1+I/

O Offset 06h).

0: No.

1: Yes.

A write to the ACPI SMI_CMD register always generates an SMI.

Table 6-33. F1BAR0+I/O Offset: SMI Status Registers (Continued)

Bit

Description