AMD Geode SC3200 User Manual

Page 175

AMD Geode™ SC3200 Processor Data Book

175

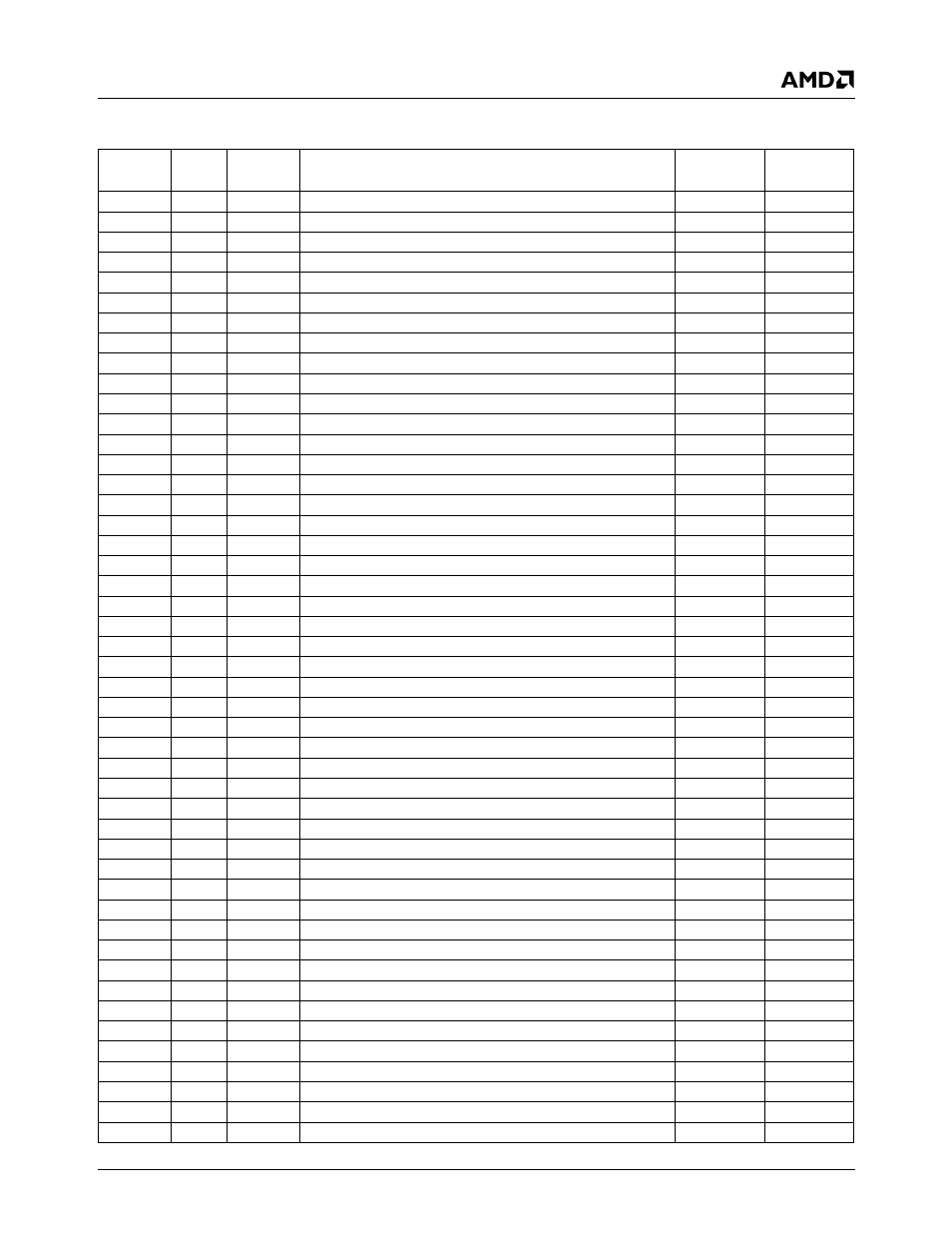

Core Logic Module - Register Summary

32581C

6Ch-6Fh

32

R/W

ROM Mask Register

0000FFF0h

70h-71h

16

R/W

IOCS1# Base Address Register

0000h

72h

8

R/W

IOCS1# Control Register

00h

73h

8

---

Reserved

00h

74h-75h

16

R/W

IOCS0 Base Address Register

0000h

76h

8

R/W

IOCS0 Control Register

00h

77h

---

---

Reserved

00h

78h-7Bh

32

R/W

DOCCS Base Address Register

00000000h

7Ch-7Fh

32

R/W

DOCCS Control Register

00000000h

80h

8

R/W

Power Management Enable Register 1

00h

81h

8

R/W

Power Management Enable Register 2

00h

82h

8

R/W

Power Management Enable Register 3

00h

83h

8

R/W

Power Management Enable Register 4

00h

84h

8

RO

Second Level PME/SMI Status Mirror Register 1

00h

85h

8

RO

Second Level PME/SMI Status Mirror Register 2

00h

86h

8

RO

Second Level PME/SMI Status Mirror Register 3

00h

87h

8

RO

Second Level PME/SMI Status Mirror Register 4

00h

88h

8

R/W

General Purpose Timer 1 Count Register

00h

89h

8

R/W

General Purpose Timer 1 Control Register

00h

8Ah

8

R/W

General Purpose Timer 2 Count Register

00h

8Bh

8

R/W

General Purpose Timer 2 Control Register

00h

8Ch

8

R/W

IRQ Speedup Timer Count Register

00h

8Dh

8

R/W

Video Speedup Timer Count Register

00h

8Eh

8

R/W

VGA Timer Count Register

00h

8Fh-92h

---

---

Reserved

00h

93h

8

R/W

Miscellaneous Device Control Register

00h

94h-95h

16

R/W

Suspend Modulation Register

0000h

96h

8

R/W

Suspend Configuration Register

00h

97h

---

---

Reserved

00h

98h-99h

16

R/W

Hard Disk Idle Timer Count Register — Primary Channel

0000h

9Ah-9Bh

16

R/W

Floppy Disk Idle Timer Count Register

0000h

9Ch-9Dh

16

R/W

Parallel / Serial Idle Timer Count Register

0000h

9Eh-9Fh

16

R/W

Keyboard / Mouse Idle Timer Count Register

0000h

A0h-A1h

16

R/W

User Defined Device 1 Idle Timer Count Register

0000h

A2h-A3h

16

R/W

User Defined Device 2 Idle Timer Count Register

0000h

A4h-A5h

16

R/W

User Defined Device 3 Idle Timer Count Register

0000h

A6h-A7h

16

R/W

Video Idle Timer Count Register

0000h

A8h-A9h

16

R/W

Video Overflow Count Register

0000h

AAh-ABh

---

---

Reserved

00h

ACh-ADh

16

R/W

Hard Disk Idle Timer Count Register — Secondary Channel

0000h

AEh

8

WO

CPU Suspend Command Register

00h

AFh

8

WO

Suspend Notebook Command Register

00h

B0h-B3h

---

---

Reserved

00h

B4h

8

RO

Floppy Port 3F2h Shadow Register

xxh

B5h

8

RO

Floppy Port 3F7h Shadow Register

xxh

B6h

8

RO

Floppy Port 1F2h Shadow Register

xxh

B7h

8

RO

Floppy Port 1F7h Shadow Register

xxh

Table 6-14. F0: PCI Header/Bridge Configuration Registers

for GPIO and LPC Support Summary (Continued)

F0 Index

Width

(Bits)

Type

Name

Reset

Value

Reference

(Table 6-29)