7 isa legacy register space, Table 6-43, Dma channel control registers – AMD Geode SC3200 User Manual

Page 295: S (table 6-43)

AMD Geode™ SC3200 Processor Data Book

295

Core Logic Module - ISA Legacy Register Space

32581C

6.4.7

ISA Legacy Register Space

The ISA Legacy registers reside in the ISA I/O address

space in the address range from 000h to FFFh and are

accessed through typical input/output instructions (i.e.,

CPU direct R/W) with the designated I/O port address and

8-bit data.

The bit formats for the ISA Legacy I/O Registers plus two

chipset-specific configuration registers used for interrupt

mapping in the Core Logic module are given in this section.

The ISA Legacy registers are separated into the following

DMA Channel Control Registers, see Table 6-43

• DMA Page Registers, see Table 6-44

• Programmable Interval Timer Registers, see Table 6-45

• Programmable Interrupt Controller Registers, see Table

• Keyboard Controller Registers, see Table 6-47

• Real-Time Clock Registers, see Table 6-48

• Miscellaneous Registers, see Table 6-49 (includes 4D0h

and 4D1h Interrupt Edge/Level Select Registers)

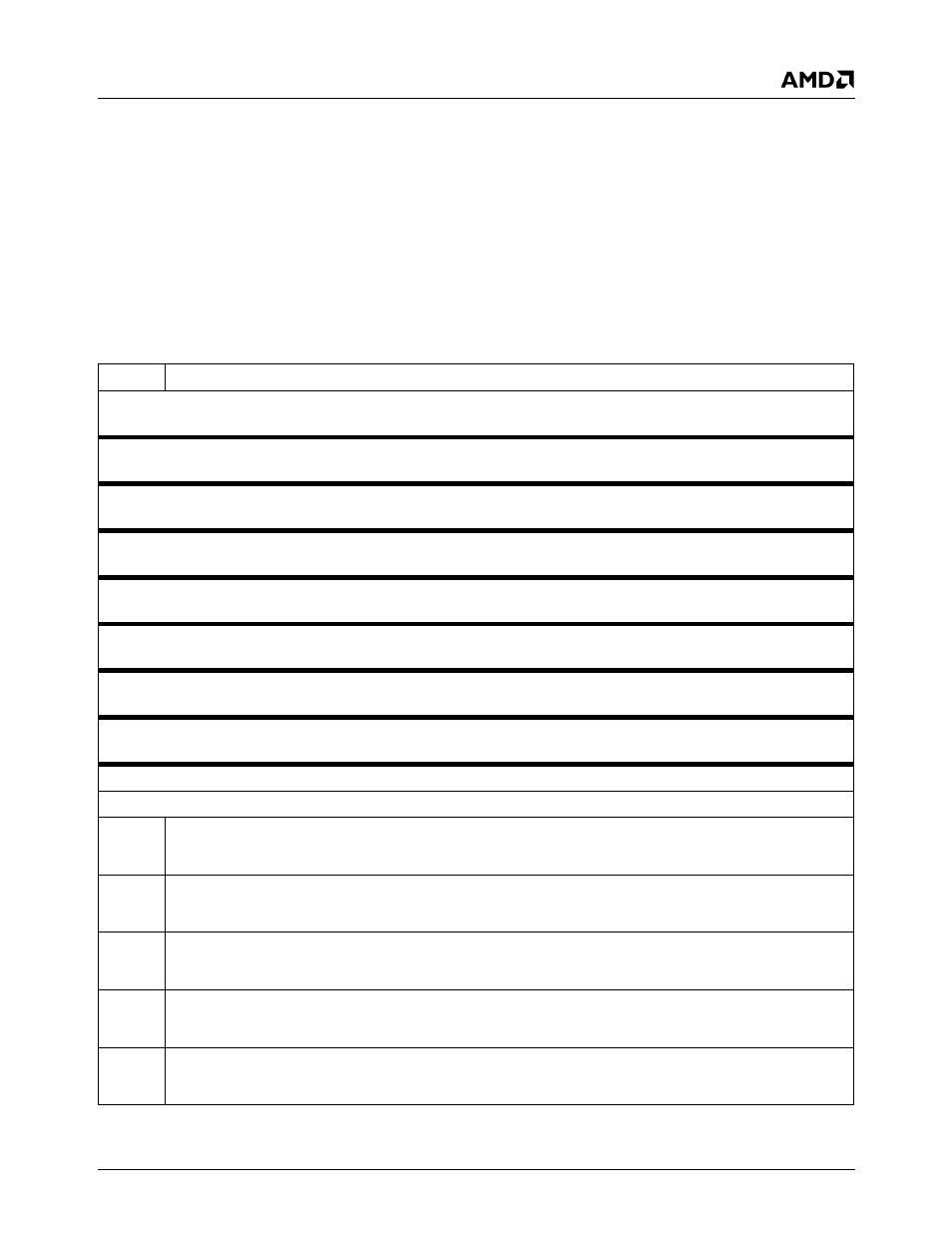

Table 6-43. DMA Channel Control Registers

Bit

Description

I/O Port 000h

DMA Channel 0 Address Register (R/W)

Written as two successive bytes, byte 0, 1.

I/O Port 001h

DMA Channel 0 Transfer Count Register (R/W)

Written as two successive bytes, byte 0, 1.

I/O Port 002h

DMA Channel 1 Address Register (R/W)

Written as two successive bytes, byte 0, 1.

I/O Port 003h

DMA Channel 1 Transfer Count Register (R/W)

Written as two successive bytes, byte 0, 1.

I/O Port 004h

DMA Channel 2 Address Register (R/W)

Written as two successive bytes, byte 0, 1.

I/O Port 005h

DMA Channel 2 Transfer Count Register (R/W)

Written as two successive bytes, byte 0, 1.

I/O Port 006h

DMA Channel 3 Address Register (R/W)

Written as two successive bytes, byte 0, 1.

I/O Port 007h

DMA Channel 3 Transfer Count Register (R/W)

Written as two successive bytes, byte 0, 1.

I/O Port 008h (R/W)

Read

DMA Status Register, Channels 3:0

7

Channel 3 Request. Indicates if a request is pending.

0: No.

1: Yes.

6

Channel 2 Request. Indicates if a request is pending.

0: No.

1: Yes.

5

Channel 1 Request. Indicates if a request is pending.

0: No.

1: Yes.

4

Channel 0 Request. Indicates if a request is pending.

0: No.

1: Yes.

3

Channel 3 Terminal Count. Indicates if TC was reached.

0: No.

1: Yes.