C/spi interface – Rainbow Electronics MAX1386 User Manual

Page 35

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I

2

C/SPI Interface

______________________________________________________________________________________

35

Set FINECH2 to 1 to load the fine DAC2 output register

with the latest write to DAC2 input registers FINE2 or

FINECAL2. This means that if FINE2 is written to after

FINECAL2, FINE2 is sent to the fine DAC2 output regis-

ter (no calibration code) when FINECH2 is set to 1. Set

HIGHCH2 to 1 to load DAC input register HIWIPE2 into

the Coarse DAC2 High Wiper register. Autocalibration

of the DAC2 high wiper occurs if the HCAL bit in

HIWIPE2 is set to 1. Set LOWCH2 to 1 to load DAC

input register LOWIPE2 into the Coarse DAC2 Low

Wiper register. Autocalibration of the DAC2 low wiper

occurs if the LCAL bit in LOWIPE2 is set to 1.

Set FINECH1 to 1 to load the fine DAC1 output register

with the latest write to DAC input registers FINE1 or

FINECAL1. If FINECAL1 is written to after FINE1,

FINECAL1 is sent to the fine DAC1 output register (with

calibration code) when FINECH1 is set to 1. Set HIGH-

CH1 to 1 to load DAC input register HIWIPE1 into the

Coarse DAC1 output register. Autocalibration of the

DAC1 high wiper occurs if the HCAL bit in HIWIPE1 is

set to 1. Set LOWCH1 to 1 to load DAC input register

LOWIPE1 into the coarse DAC1 output register.

Autocalibration of the DAC1 low wiper occurs if the

LCAL bit in LOWIPE1 is set to 1.

SCLR (Write)

Write to the Software Clear register to reset the DACs

and FIFO to their POR states (see Table 19). Write to the

Software Clear register by sending the appropriate write

command byte followed by data bits D15–D0. Bits

D15–D10 are don’t care. A write to bits D5–D0 in the

Software Clear register immediately changes the appro-

priate DAC output to its power-on state (regardless of

LDAC). To reset all registers at once, set FULLRESET to

0 and ARMRESET to 1. Next set FULLRESET to 1 and

ARMRESET to 0. This 2-byte reset operation protects the

registers from being fully reset by inadvertent user

writes. After a full reset, the device is in shutdown mode

and the SSHUT register needs to be written to for full

operation.

Set CLFIFO to 1 to clear the entire 15-word FIFO and

FIFO-associated flag bits in the Flag register. Set

HIGHCL2 to 1 to reset the Coarse DAC2 High Wiper

Output and Input registers to their POR states. Set

LOWCL2 to 1 to reset the coarse DAC2 High Wiper

Output and Input registers to their POR states. Set

FINECL1 to 1 to reset Fine DAC1 Output and Input reg-

isters to their POR states. Set HIGHCL1 to 1 to reset

the Coarse DAC1 High Wiper Output and Input regis-

ters to their POR states. Set LOWCL1 to 1 to reset the

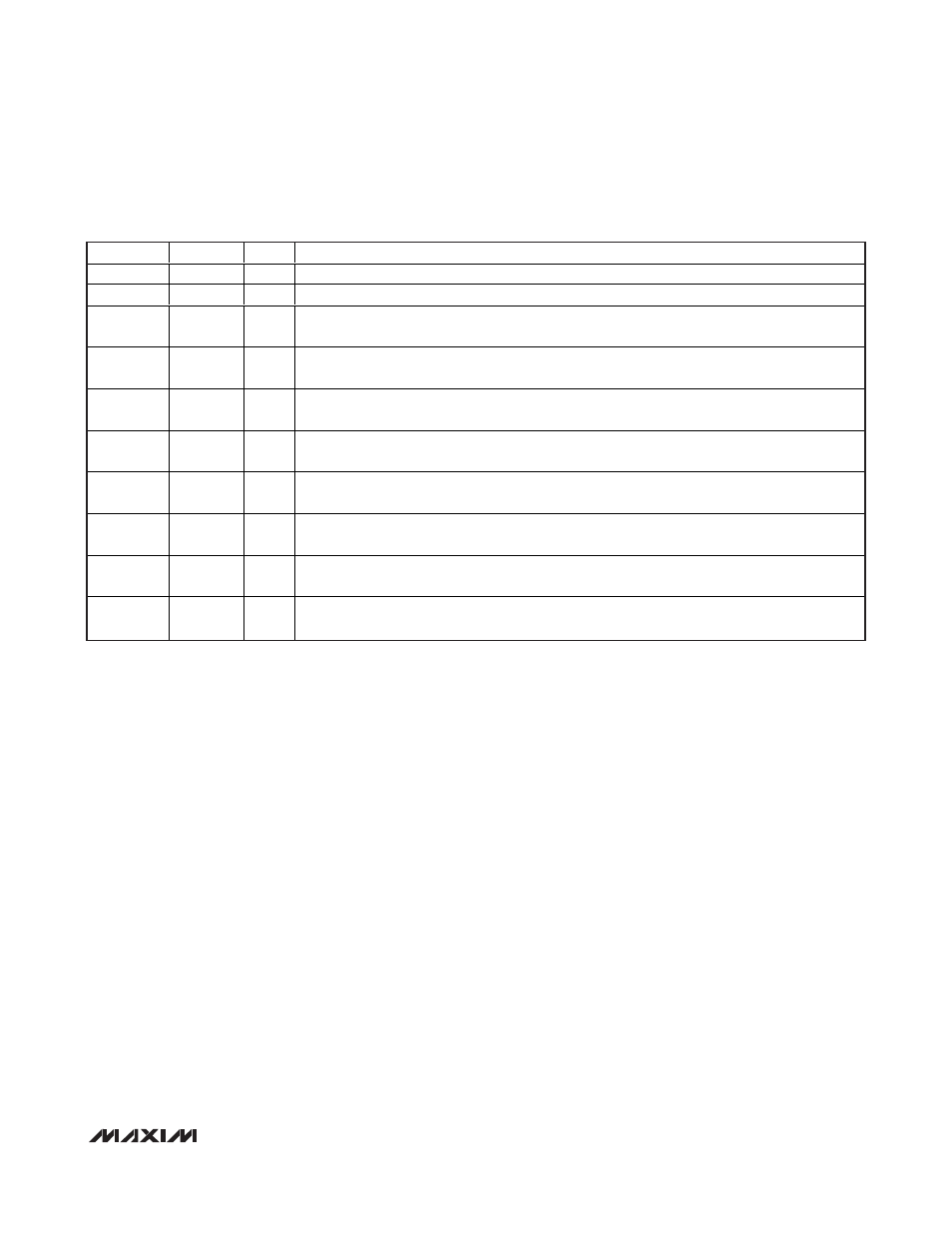

BIT NAME

DATA BIT

POR

FUNCTION

X

D15–D12

X

Don’t care

Reserved

D11–D8

0

Reserved; set these bits to 0

CONCONV

D7

0

1 = Continuous conversions (repeated scans)

0 = Noncontinuous conversions (one scan)

ADCSEL2

D6

0

1 = Select voltages at ADCIN2 to be converted

0 = Do not select voltages at ADCIN2 to be converted

IEXT2

D5

0

1 = Select voltages at PGAOUT2 to be converted

0 = Do not select voltages at PGAOUT2 to be converted

TEXT2

D4

0

1 = Select temperature at remote diode 2 to be converted

0 = Do not select temperature at remote diode 2 to be converted

ADCSEL1

D3

0

1 = Select voltages at ADCIN1 to be converted

0 = Do not select voltages at ADCIN1 to be converted

IEXT1

D2

0

1 = Select voltages at PGAOUT1 to be converted

0 = Do not select voltages at PGAOUT1 to be converted

TEXT1

D1

0

1 = Select temperature at remote diode 1 to be converted

0 = Do not select temperature at remote diode 1 to be converted

TINT

D0

0

1 = Select internal temperature of device to be converted

0 = Do not select internal temperature of device to be converted

Table 16. ADCCON (Write)