C/spi interface, Table 7. dcfig (read/write), Table 7a. gain-setting modes – Rainbow Electronics MAX1386 User Manual

Page 30: Table 7b. clock modes, Table 7c. adc reference selection

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I

2

C/SPI Interface

30

______________________________________________________________________________________

Alarm Modes

section). Setting ALARMCMP does not

affect SAFE1 and SAFE2 outputs. Program

ALARMHYST1 and ALARMHYST0 to set the amount of

built-in hysteresis used in window-threshold mode.

See the

ALARM Output

and

SAFE1/SAFE2 Outputs

sections for a description of the relationship between

ALARM and SAFE1 and SAFE2. Set TALARM2 to 1 to

allow channel 2 temperature measurements to control

the state of SAFE2 and ALARM based on channel 2

temperature thresholds. Set TWIN2 to 0 to enable hys-

teresis-threshold mode and to 1 to enable window-

threshold mode for channel 2 temperature

measurements (see the

Alarm Modes

section). Set

IALARM2 to 1 to allow channel 2 current measurements

to control the state of SAFE2 and ALARM based on

channel 2 current thresholds. Set IWIN2 to 0 to enable

hysteresis-threshold mode and to 1 to enable window-

threshold mode for channel 2 current measurements.

Set TALARM1 to 1 to allow channel 1 temperature mea-

surements to control the state of SAFE1 and ALARM

based on channel 1 temperature thresholds. Set TWIN1

to 0 to enable hysteresis-threshold mode and to 1 to

enable window-threshold mode for channel 1 tempera-

ture measurements (see the

Alarm Modes

section). Set

IALARM1 to 1 to allow channel 1 current measurements

to control the state of SAFE1 and ALARM based on

channel 1 current thresholds. Set IWIN1 to 0 to enable

hysteresis-threshold mode and to 1 to enable window-

threshold mode for channel 1 current measurements.

HIWIPE1 and HIWIPE2 (Read/Write)

Write to the Coarse DAC1/DAC2 High Wiper Input reg-

ister by sending the appropriate write command byte

followed by data bits D15–D0 (see Table 9). Bits

D14–D8 are don’t care. Read the Coarse DAC1/DAC2

High Wiper Input register by sending the appropriate

read command byte. The DAC output is not updated

until an LDAC command is issued, at which point the

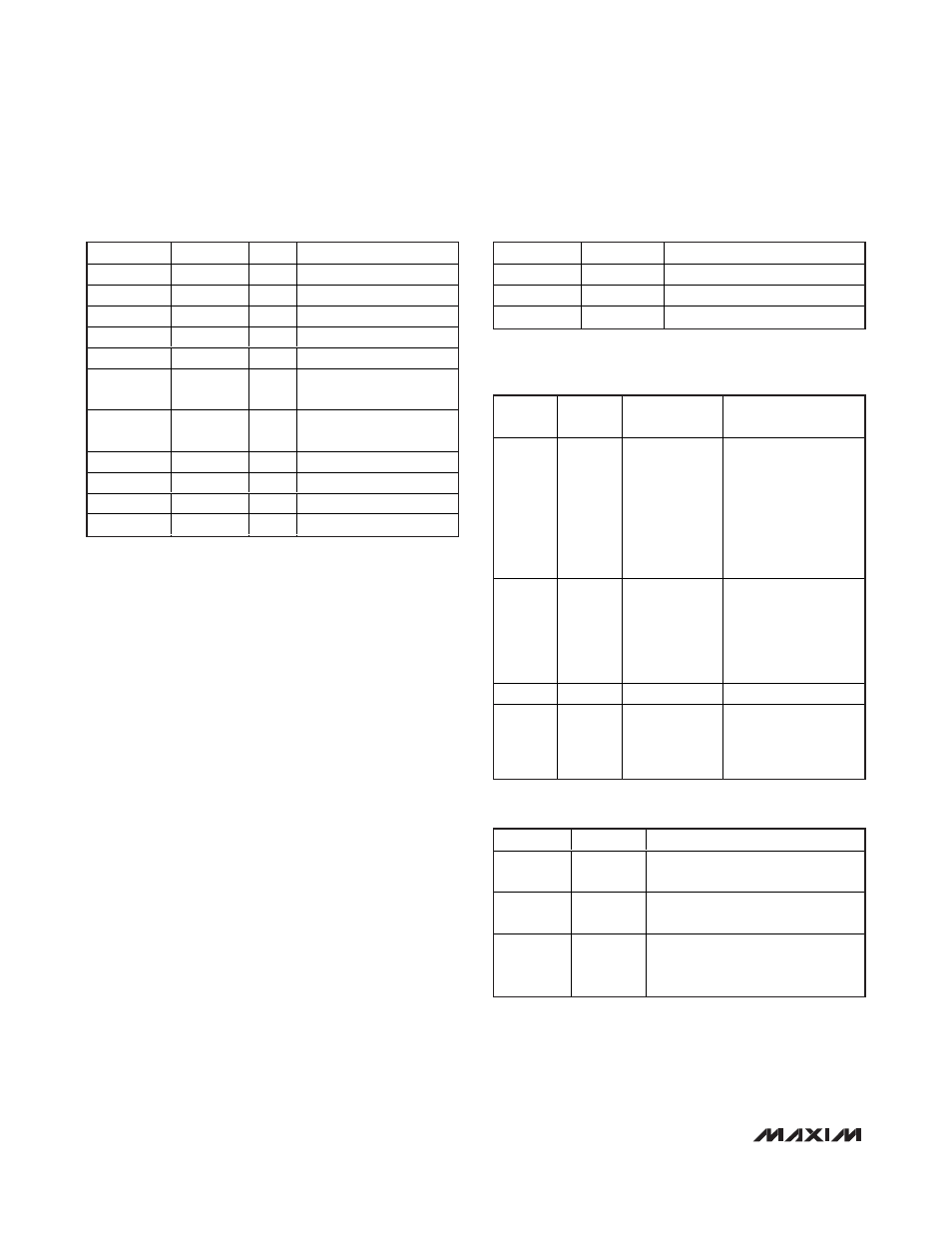

BIT NAME

DATA BIT

POR

FUNCTION

X

D15–D10

X

Don’t care

PG2SET1

D9

0

PGA 2 gain-setting

PG2SET0

D8

0

PGA 2 gain-setting

PG1SET1

D7

0

PGA 1 gain-setting

PG1SET0

D6

0

PGA 1 gain-setting

CKSEL1

D5

0

Clock mode and

CNVST

configuration

CKSEL0

D4

0

Clock mode and

CNVST

configuration

REFADC1

D3

0

ADC reference select

REFADC0

D2

0

ADC reference select

REFDAC1

D1

0

DAC reference select

REFDAC0

D0

0

DAC reference select

Table 7. DCFIG (Read/Write)

PG_SET1

PG_SET0

FUNCTION

0

0

PGA_ gain of 2

0

1

PGA_ gain of 10

1

X

PGA_ gain of 25

Table 7a. Gain-Setting Modes

X = Don’t care.

CKSEL1

CKSEL0

CONVERSION

CLOCK

ACQUISITION/

SAMPLING

0

0

Internal

Internally timed

acquisitions and

conversions.

Conversions started by

a write to the Analog-

to-Digital Conversion

register or setting the

CONCONV bit.

0

1

Internal

Internally timed

acquisitions and

conversions.

Conversions begin with

a high-to-low transition

at

CNVST.

1

0

—

Reserved. Do not use.

1

1

Internal

Externally timed

acquisitions by

CNVST. Conversions

internally timed.

Table 7b. Clock Modes

REFADC1

REFADC0

DESCRIPTION

0

X

External. Bypass REFADC with a

0.1µF capacitor to AGND.

1

0

Internal. Leave REFADC

unconnected.

1

1

Internal. Connect a 0.1µF capacitor

to REFADC for better noise

performance.

Table 7c. ADC Reference Selection

X = Don’t care.