Configuration bits – Rainbow Electronics T89C5121 User Manual

Page 68

68

A/T8xC5121

4164G–SCR–07/06

The only mean to remove the security level 2 is to send a Full Chip Erase command.

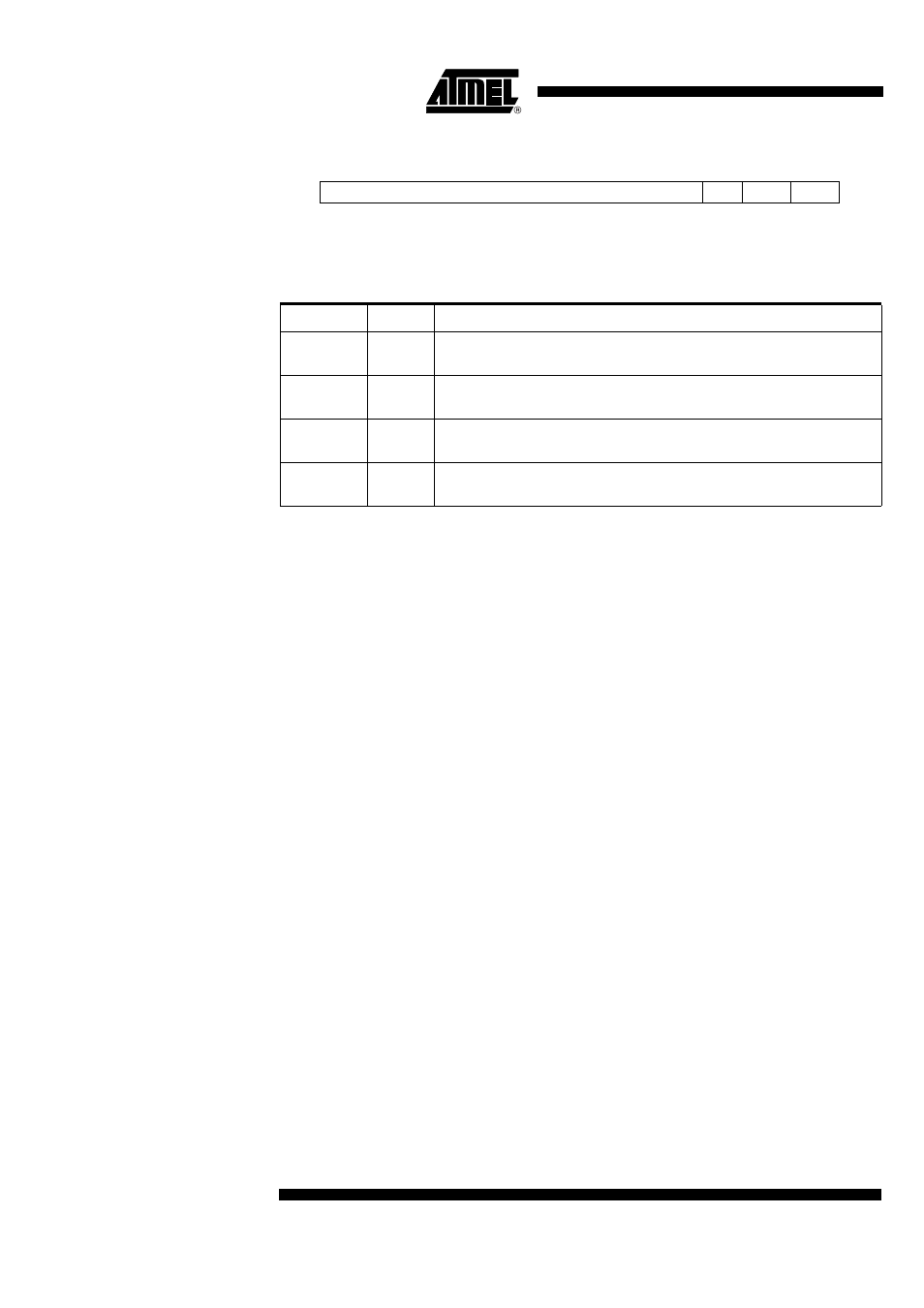

Table 48. Synthesis of Security Mechanisms

Configuration Bits

The Bootloader tests that TWI components are connected as slave components on the

TWI external bus and later in the algorithm if characters are received on the UART input.

This default configuration can be changed, after a first programming, in order:

–

to disable new programming in download mode from external serial

EEPROM to disable ISP programming using UART and

–

to avoid any conflict with the target hardware on external TWI bus or UART.

This can be configured with the two higher bits of the SSB Byte detailed in the previous

paragraph.

The bit 7 is used to bypass (if 0) the External TWI Acknowledge test.

The bit 6 is used to bypass (if 0) the UART receipt test.

These two bypass modes can be disabled if a level 0 is applied on, respectively, P3.5

and P3.6 pins. This allows to force and use ISP even if the device has been configured

as programmed device.

Source

Function

Protection

Internal

EEPROM

Write

The first protection level of the SSB Byte IN the internal EEPROM protects

against ISP Write command

Internal

EEPROM

Read

The second protection level of the SSB Byte IN the internal EEPROM protects

against ISP Read commands

CRAM

Write

The first protection level of the SSB Byte IN the internal EEPROM protects

against ISP Write command in CRAM

CRAM

Read

The second protection level of the SSB Byte IN the CRAM protects against ISP

Read commands

Data Bytes

SSB

Address

3FFD