Clock prescaler, Clock control registers, Clock prescaler register – Rainbow Electronics T89C5121 User Manual

Page 24

24

A/T8xC5121

4164G–SCR–07/06

Clock Prescaler

Before supplying the CPU and the peripherals, the main clock is divided by a factor 2 to

30 to reduce the CPU power consumption. This factor is controlled with the CKRL

register.

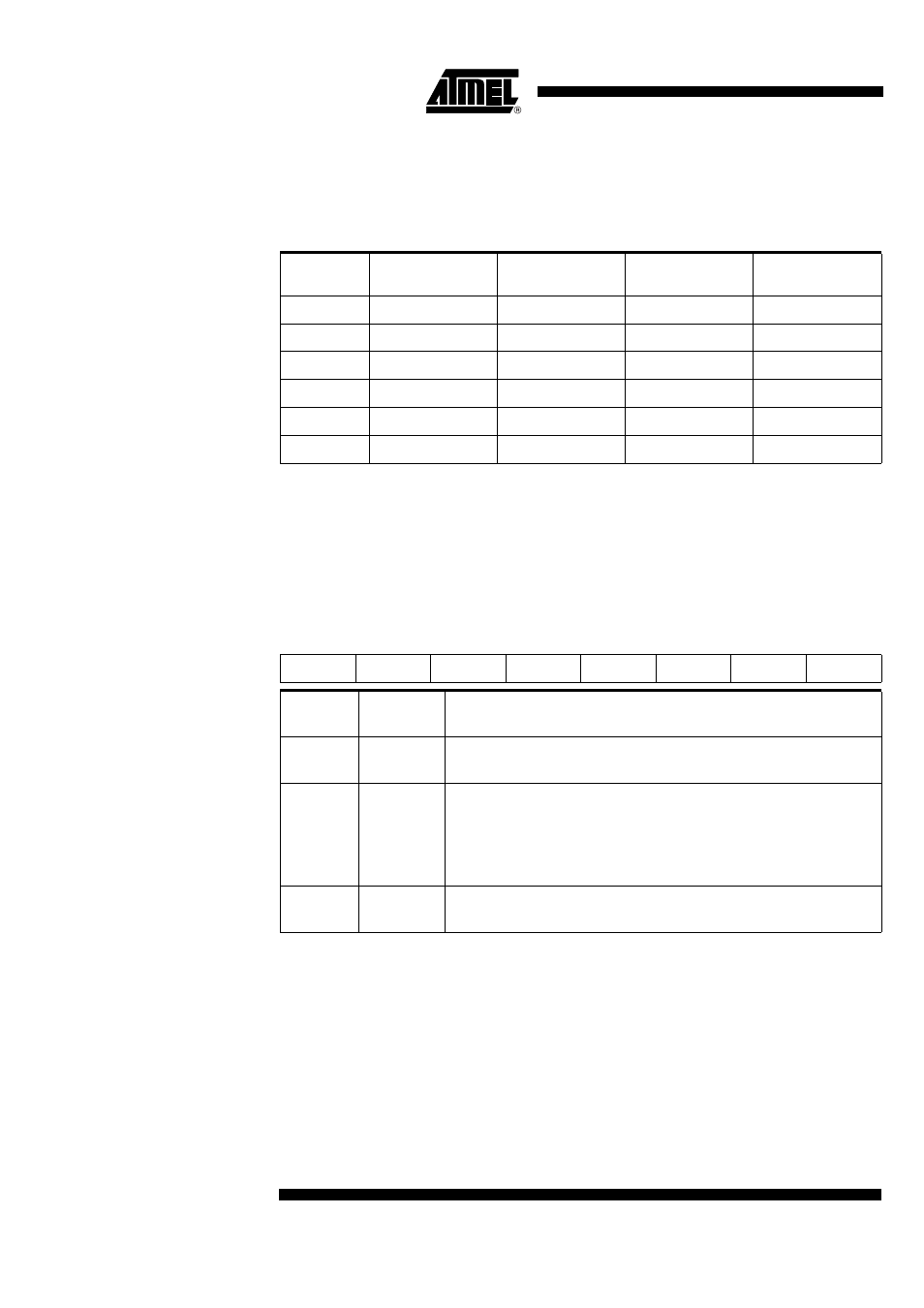

Table 7. Examples of Factors

Clock Control Registers

Clock Prescaler Register

This register is used to reload the clock prescaler of the CPU and peripheral clock.

Table 8. CKRL Register

CKRL - Clock Reload Register (97h)

Reset Value = XXXX 111Xb

XTAL (MHz)

X2 CPU CKCON0

CKRL Value

Prescaler Factor

F

CLK_CPU,

F

CLK_Periph

(MHz)

16

0 (reset mode)

07h

1

8

16

1 (X2 mode)

07h

1

16

16

1

07h

1

16

16

0

07h

1

8

16

0

06h

2

4

16

1 06h

2

8

7

6

5

4

3

2

1

0

-

-

-

-

CKRL

CKRL

CKRL

-

Bit

Number

Bit

Mnemonic

Description

7 - 4

-

Reserved

The value read from this bit is indeterminate. Do not set this bit.

3 - 1

CKRL

Clock Reload Register

Prescaler value

XXXX 000Xb: CKRL=7 and Division factor equals 14

XXXX 110Xb: CKRL=6 and factor equals 2

XXXX 111Xb: CKRL=7 and division factor equals 1

0

-

Reserved

The value read from this bit is indeterminate. Do not set this bit.