Dc/dc clock, Clock control register, Clock prescaler – Rainbow Electronics T89C5121 User Manual

Page 27

27

A/T8xC5121

4164G–SCR–07/06

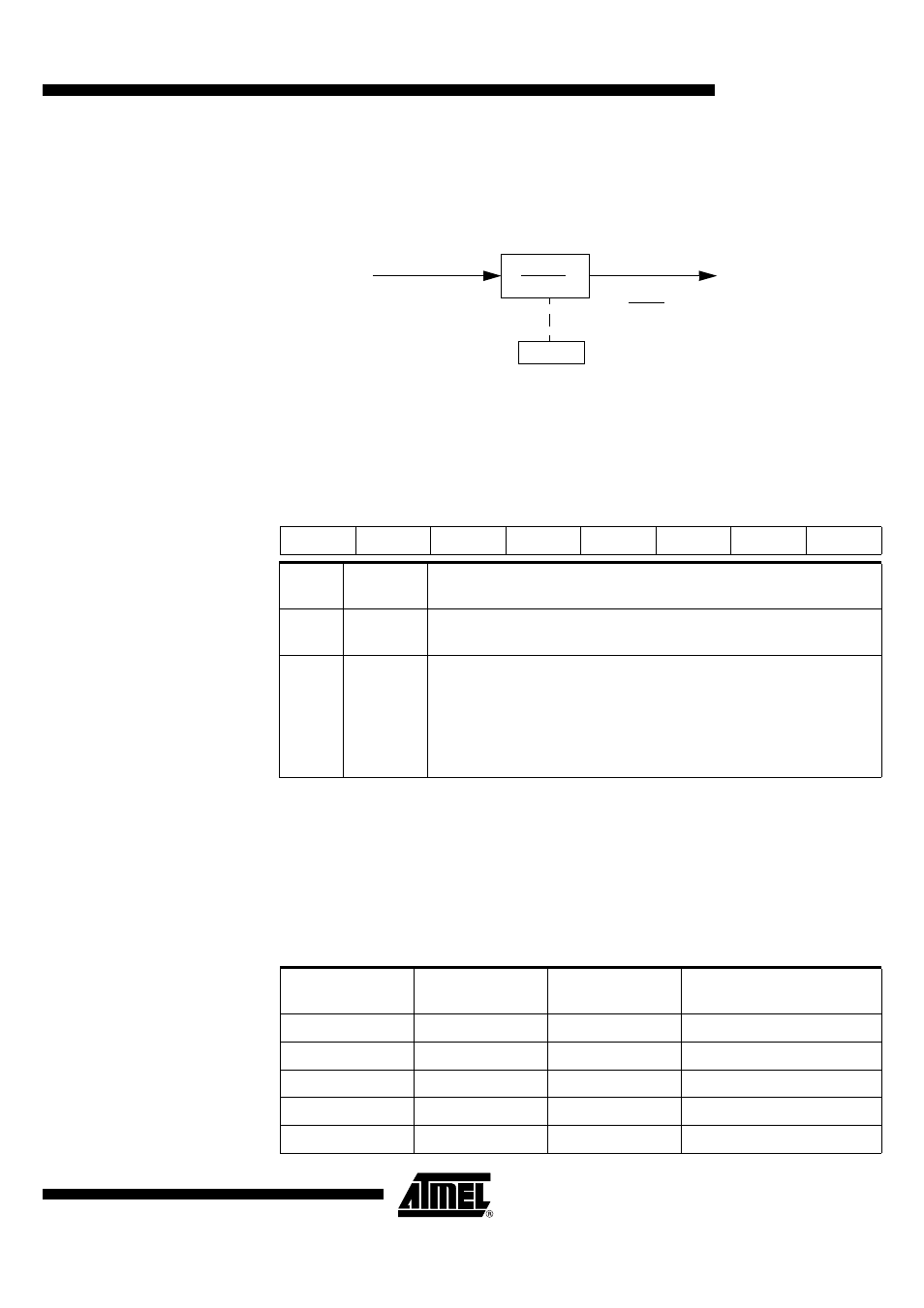

DC/DC Clock

The DC/DC block needs a clock with a 50% duty cycle. The frequency must also respect

a value between 3.68 MHz and 4 MHz. The first requirement imposes a divider in the

clock path and the second constraint is solved with the use of a prescaler.

Figure 13. Functional Block Diagram

Clock Control Register

This register is used to reload the clock prescaler of the DC/DC converter clock.

Table 11. DCCKPS Register

DCCKPS - DC/DC converter Reload Register (BFh)

Reset Value = XXXX XX11b

Clock Prescaler

Before supplying the DC/DC block, the oscillator clock is divided by a factor 2 to 5 to

adapt the clock needed by the DC/DC converter. This factor is controlled with the

DCCKPS register.

The prescaler factor must be chosen to match the requirement range which is 4MHz.

Table 12. Examples of Factors

1

F

CLK_DC/DC

F

OSC

F

OSC

2 to 5

(2 to 5)

DCCKPS

Address BFh

7

6

5

4

3

2

1

0

-

-

-

-

-

-

DCCKPS

DCCKPS

Bit

Number

Bit

Mnemonic

Description

7:2

-

Reserved

Do not use write those bits

1:0

DCCKPS

Clock Reload Register

Prescaler value

00b: Division factor equals 2

01b: division factor equals 3

10b: division factor equals 4

11b: division factor equals 5 (reset value which minimize the consumption)

XTAL (MHz)

DCCKPS Value

Prescaler

Factor

DC/DC Converter CLK (MHz)

8

00h

2

4

12

01h

3

4

14.756

02h

4

3.689

16

02h

4

4

20

03h

5

4