Rainbow Electronics DS28DG02 User Manual

Page 4

DS28DG02: 2kb SPI EEPROM with PIO, RTC, Reset, Battery Monitor, and Watchdog

4 of 33

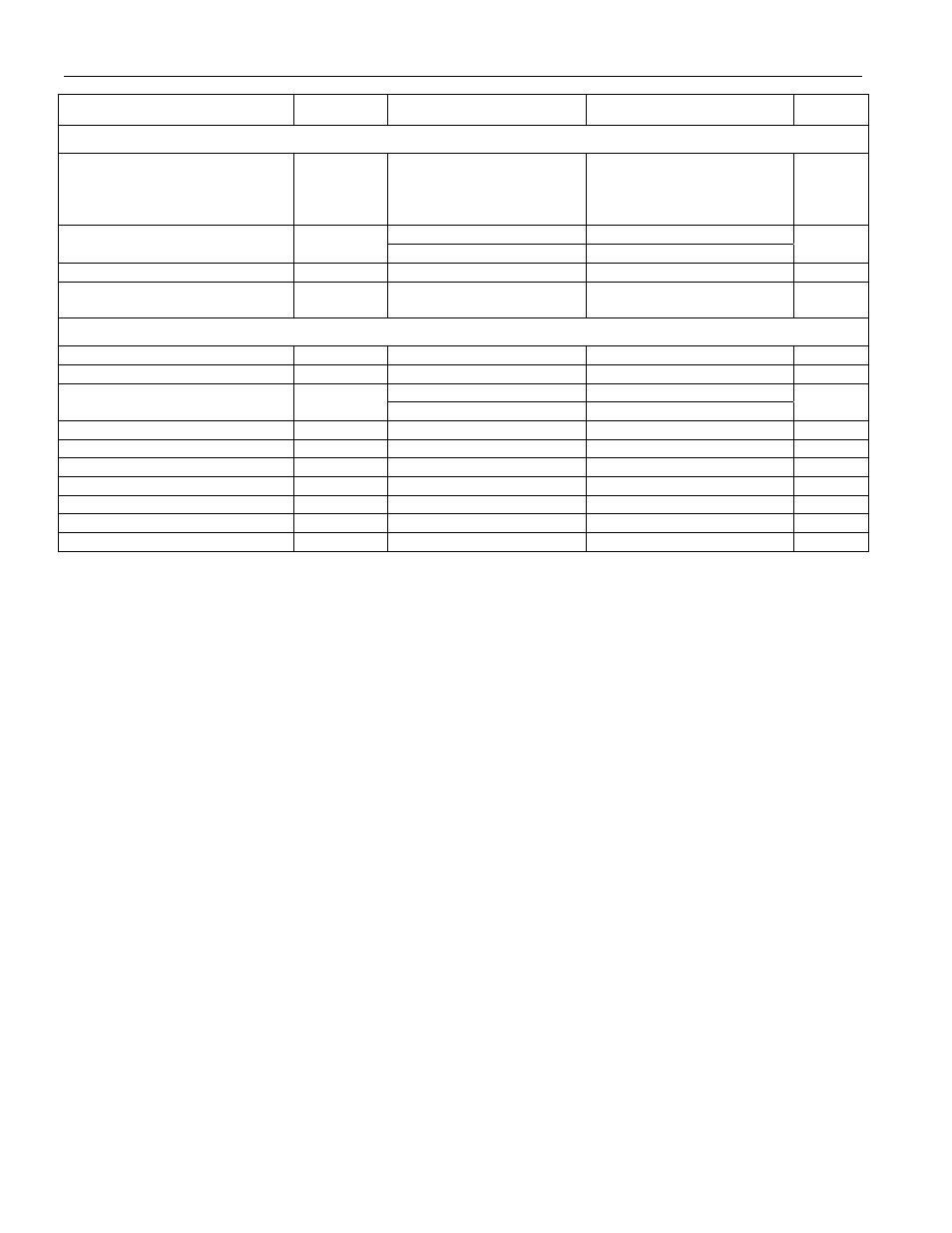

PARAMETER SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

BATTERY MONITOR (See Figure 8)

V

BAT

Trip Point

V

BTP

Measured with V

BAT

falling; trip point is user

programmable

2.25

2.03

1.80

1.58

2.31

2.08

1.85

1.62

2.38

2.14

1.90

1.66

V

+25°C -1.5

+1.5

V

BAT

Monitor Trip-Point

Tolerance

V

TRIPTOL

-40°C to +85°C

-2.5

+2.5

%V

BTP

Battery Test Load Current

I

LOAD

7.5

20

µA

Battery Test Duration

t

BTPW

Load applied to battery

(Notes 5, 16)

2 s

SPI INTERFACE TIMING (See Figures 9, 10)

CSZ Setup Time

t

CSS

(Note

5)

0.4

µs

CSZ Hold Time

t

CSH

(Note

5)

0.4

µs

Normal communication

0.25

CSZ Standby Pulse Width

(Note 5)

t

CPH

(Note 17)

2.0

µs

CSZ to High-Z at SO

t

CHZ

0.25 µs

SCK Clock Frequency

f

CLK

2 MHz

Data Setup Time

t

DS

(Note

5)

50

ns

Data Hold Time

t

DH

(Note

5)

50

ns

SCK Rise Time

t

SCKR

(Note

5)

1

µs

SCK Fall Time

t

SCKF

(Note

5)

1

µs

Output Valid time

t

V

(Note

5)

0 120 ns

Note 1:

If no battery is used, connect the V

BAT

pin to V

CC

. The RTC is powered by V

BAT

if V

CC

falls below V

CCmin

.

Note 2:

To the first order, this current is independent of the supply voltage value.

Note 3:

Nominal values: 3.3V -5%, set at factory. Measured with V

CC

falling; for V

CC

rising, the actual threshold is

V

TRIP

+ V

HYST

.

Note 4:

This specification is valid for each 16-byte memory page.

Note 5:

Not production tested. Either guaranteed by design (GBD) or guaranteed by a reliability study (EEPROM lifetime

parameters).

Note 6:

EEPROM writes can become nonfunctional after the data-retention time is exceeded. Long-time storage at

elevated temperatures is not recommended; the device can lose its write capability after 10 years at +125°C or 40

years at +85°C.

Note 7:

Valid with 32KHz crystal, 12.5pF, ESR

≤ 45kΩ, +25°C.

Note 8:

Total PIO sink and source currents through all PIO pins must be externally limited to less than the absolute

maximum rating of 270mA minus 1.5mA for EEPROM programming and SPI communication. Exceeding the

absolute maximum rating can cause damage.

Note 9:

Assumes the configuration of the system and the part is such that changing GOV (0 ≤ i ≤ 11) between ‘b1 and

‘b0 switches between sourcing no current and sinking the absolute maximum current at the PIO pin. The limit

refers to the switching time between sinking 20% of the DC current and 80% of the DC current. The same is true

for changing between 'b0 and 'b1 causing the part to switch from sinking no current to sourcing the absolute

maximum current at the PIO pin.

Note 10:

Each output pin transitions in 1µs with a pause of 1µs before the next pin transitions.

Note 11:

All PIO are tri-stated at beginning of reset prior to setting to power-on values.

Note 12:

If the part has battery power (normal case) the active pulldown of RSTZ is supported by the battery.

Note 13:

If V

BAT

is tied to V

CC

(no battery supply) the state of the RSTZ pulldown transistor is not guaranteed when V

CC

falls

below V

POR

.

Note 14:

Threshold refers to the manual reset function obtained by forcing RSTZ low.

Note 15:

Transient response to a step on V

CC

from above V

TRIP

down to (V

TRIP

- 1mV). Glitches on V

CC

that are shorter than

t

DELmin

are guaranteed to be suppressed, regardless of their amplitude. Glitches on V

CC

that are longer than t

DELmax

are guaranteed not to be suppressed. This parameter is tested at high V

CC

and guaranteed by design at low.

Note 16:

If enabled, this test takes place every hour on the hour. The battery voltage is compared to V

BTP

during the second

half of the t

BTPW

window. The timing is controlled by the RTC.

Note 17:

Extended duration applies to the following cases:

1) Aborted WREN, WRDI, RDSR, and WRSR command.

2) WRITE command aborted before transmitting the first complete data byte after command and address.

3) READ command aborted before reading the first complete data byte after command and address.

4) Read aborted before the end of a byte.