Rainbow Electronics DS28DG02 User Manual

Page 19

DS28DG02: 2kb SPI EEPROM with PIO, RTC, Reset, Battery Monitor, and Watchdog

19 of 33

Principles of Operation

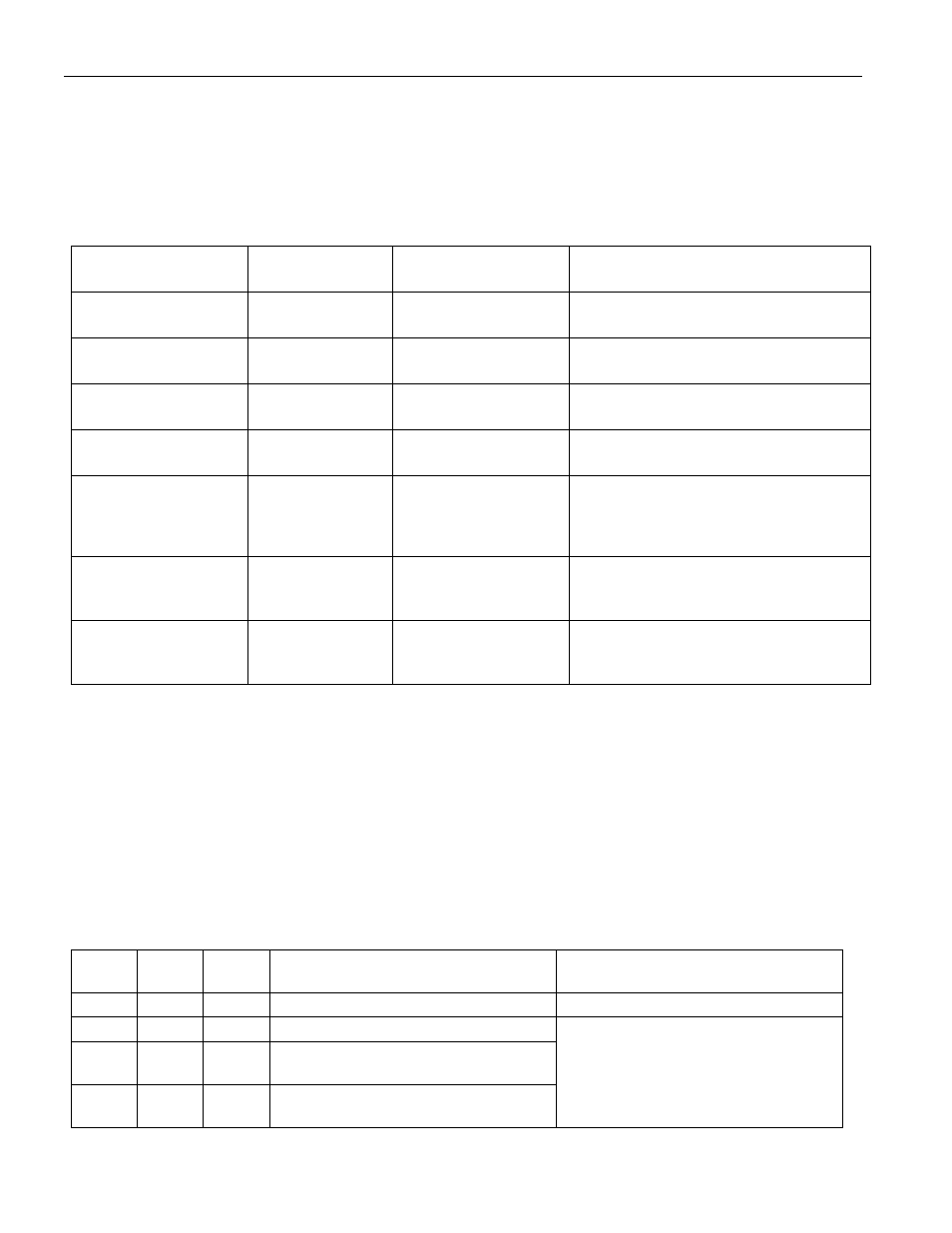

The first byte that the DS28DG02 receives from the master after a falling edge on CSZ is interpreted as an instruc-

tion. The DS28DG02 supports a set of seven instructions, which are summarized in Figure 11. The protocol uses

only a single address byte. The 9th address bit necessary to access addresses of 100h and higher is included in

the instruction code, marked as "X".

Figure 11. SPI Instruction Set

INSTRUCTION NAME

INSTRUCTION

CODE

PROTOCOL PURPOSE

WREN

Write Enable

0000 0110b

Tx Instruction Code

To set the WEN bit in the SPI Status

register. (Enable Writes to Memory)

WRDI

Write Disable

0000 0100b

Tx Instruction Code

To clear the WEN bit in the SPI Status

register. (Disable Writes to Memory)

WRSR

Write Status Register

0000 0001b

Tx Instruction Code

Tx SPI Status Byte

To update the SPI Status register.

RDSR

Read Status Register

0000 0101b

Tx Instruction Code

Rx SPI Status Byte

To read SPI Status register; to detect the

end of an EEPROM write cycle.

RFSH

Refresh Registers

0000 0111b

Tx Instruction Code

To update the SRAM registers at

addresses 120h to 125h with their

power-on default values without power-

cycling.

WRITE

Write to Memory

0000 X010b

Tx Instruction Code

Tx Address Byte

Tx Data Byte(s)

To write to the memory, register, PIOs,

or the

RTC

, depending on the specified

address.

READ

Read Memory

0000 X011b

Tx Instruction Code

Tx Address Byte

Rx Data Byte(s)

To read from the memory, register, PIOs,

or the

RTC

, depending on the specified

address.

The first four instructions relate to the SPI Status register, which contains control bits and a status bit. The SPI

Status register is not memory-mapped and can only be updated through SPI instructions. It holds several bits that

control an elaborate scheme to prevent inadvertent changes of data stored in the device:

A write-enable bit WEN that needs to be set through a write-enable instruction WREN before a write instruction

is accepted. The WEN bit is automatically cleared after successful execution of a write instruction.

Hardware write-protection of b7:b2 (nonvolatile bits) of the SPI Status register through the write-protect enable

bit WPEN in conjunction with the logic state at the WPZ pin.

Write-Protect bits for memory blocks and the registers from address 120h and higher.

The combined effect of WEN, WPEN, and WPZ is summarized in Table 2. The full description of the SPI Status

register bit functions is found in Figure 12.

Table 2. Write Protection Summary

WEN

BIT

WPEN

BIT

WPZ

PIN

SPI STATUS REGISTER

MEMORY

0

x

x

Write-protected (because WEN = 0).

Write-protected (because WEN = 0).

1

0

x

Writeable (because WPEN = 0).

1 1 0

Write-protected (because WPEN = 1

AND the WPZ pin is at logic 0).

1 1 1

Writable (because WPEN = 1 AND the

WPZ pin is at logic 1).

Conditional write access:

BP1:BP0 control protection of

addresses 00h to FFh.

RPROT controls protection of

addresses 120h and higher.