Detailed description—spi instruction set – Rainbow Electronics DS28DG02 User Manual

Page 20

DS28DG02: 2kb SPI EEPROM with PIO, RTC, Reset, Battery Monitor, and Watchdog

20 of 33

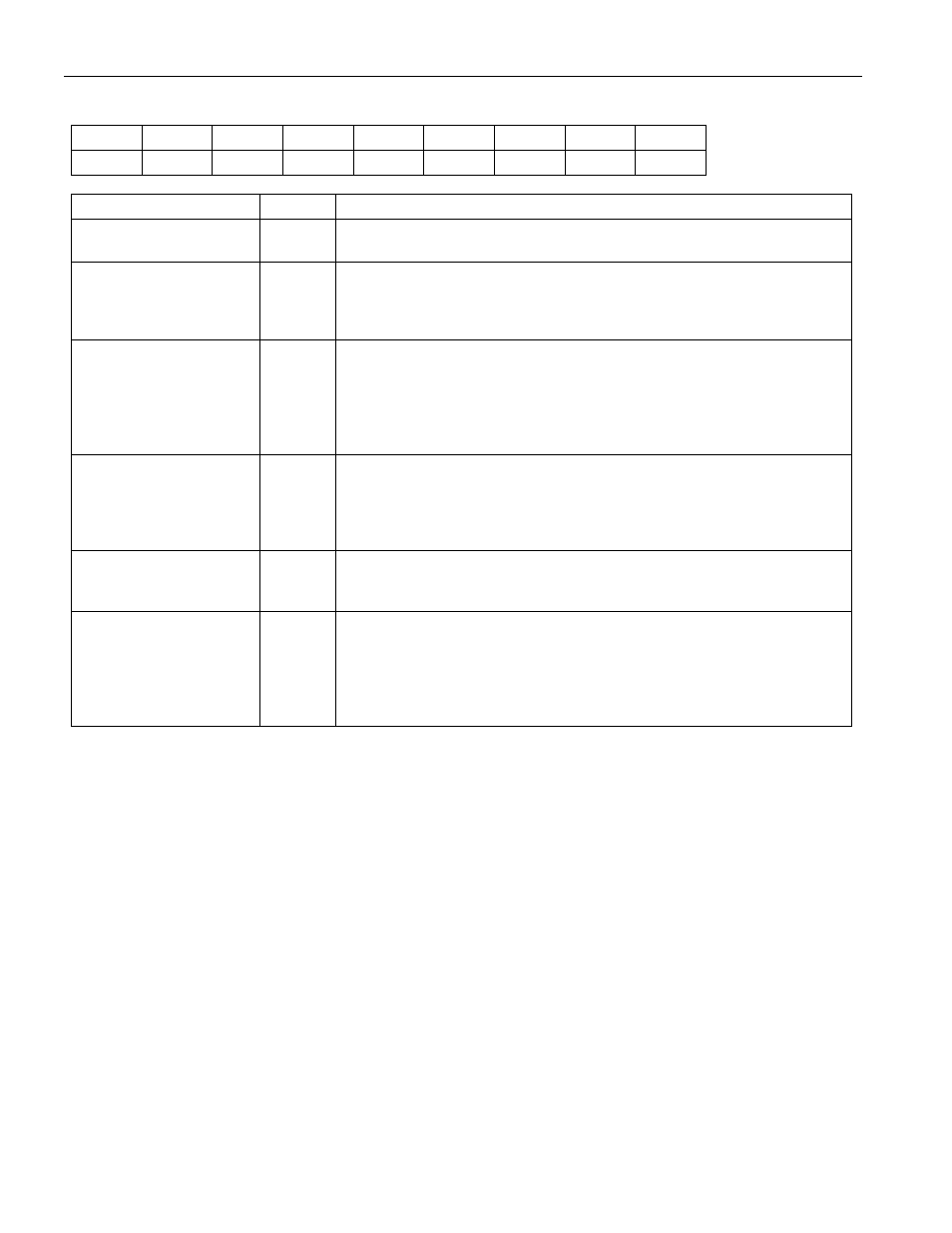

Figure 12. SPI Status Register

ADDR

b7 b6 b5 b4 b3 b2 b1 b0

N/A

WPEN

RPROT

WD1 WD0 BP1 BP0 WEN RDYZ

BIT DESCRIPTION

BIT(S)

DEFINITION

RDYZ: Ready (Read-

Only Bit)

b0

Indicates whether an EEPROM write cycle is in progress.

Legend

:

0 Î ready (normal state); 1 Î write cycle in progress

WEN: Write Enabled

(Read-Only Bit)

b1

Indicates whether the device will accept a WRITE instruction; set

through the WREN instruction; cleared through the WRDI instruction or

completion of a valid WRITE or a valid WRSR instruction.

Legend

:

0 Î write disabled (power-on default); 1 Î write enabled

BP1:BP0: Block Write

Protect

b3:b2

These bits specify which of the four user memory blocks are write-

protected (independent of WPEN and WPZ).

Legend

:

00b Î not protected (factory default)

01b

Î

block 3 (0C0h to 0FFh) protected

10b

Î

blocks 2 and 3 (080h to 0FFh) protected

11b

Î

blocks 0 to 3 (000h to 0FFh) protected

WD1:WD0: Watchdog

Timeout

b5:b4

These bits specify the duration of the watchdog timeout if the watchdog

is enabled (WDE at address 134h = 1).

Legend

:

00b Î 1.64s (factory default); 01b Î 820ms

10b

Î

410ms; 11b Î 200ms

These are nominal values; for tolerances see Electrical Characteristics.

RPROT: Register

Protection

B6

Specifies whether the writeable addresses in the range of 120h and

higher are write-protected (independent of WPEN and WPZ).

Legend

:

0 Î not protected (factory default); 1 Î protected

WPEN: Hardware Write

Protect Enable

b7

Specifies whether b7:b2 of the SPI Status register (nonvolatile bits) are

writeable or whether the WPZ pin state controls the write-protection.

Legend:

0 Î writeable (factory default)

1

Î

protection controlled by WPZ pin state

If WPEN = 1 and WPZ pin state is 0 the SPI Status register is write-

protected and a WRSR instruction is not valid.

DETAILED DESCRIPTION—SPI INSTRUCTION SET

WREN Write Enable

Before any write access to the device, the WEN bit in the SPI Status register must be set. The only way to set this

bit is through the write-enable instruction. The WEN bit is cleared when the device powers up, after the successful

execution of a write access instruction (WRSR or WRITE) and through WRDI. Figure 13 shows the instruction’s

timing diagram for both SPI communication modes.

WRDI Write Disable

The WRDI instruction can be used to clear the WEN bit of the SPI Status register, e.g., after an unsuccessful write

access instruction. Figure 14 shows the instruction’s timing diagram for both SPI communication modes.