Rainbow Electronics DS28DG02 User Manual

Page 13

DS28DG02: 2kb SPI EEPROM with PIO, RTC, Reset, Battery Monitor, and Watchdog

13 of 33

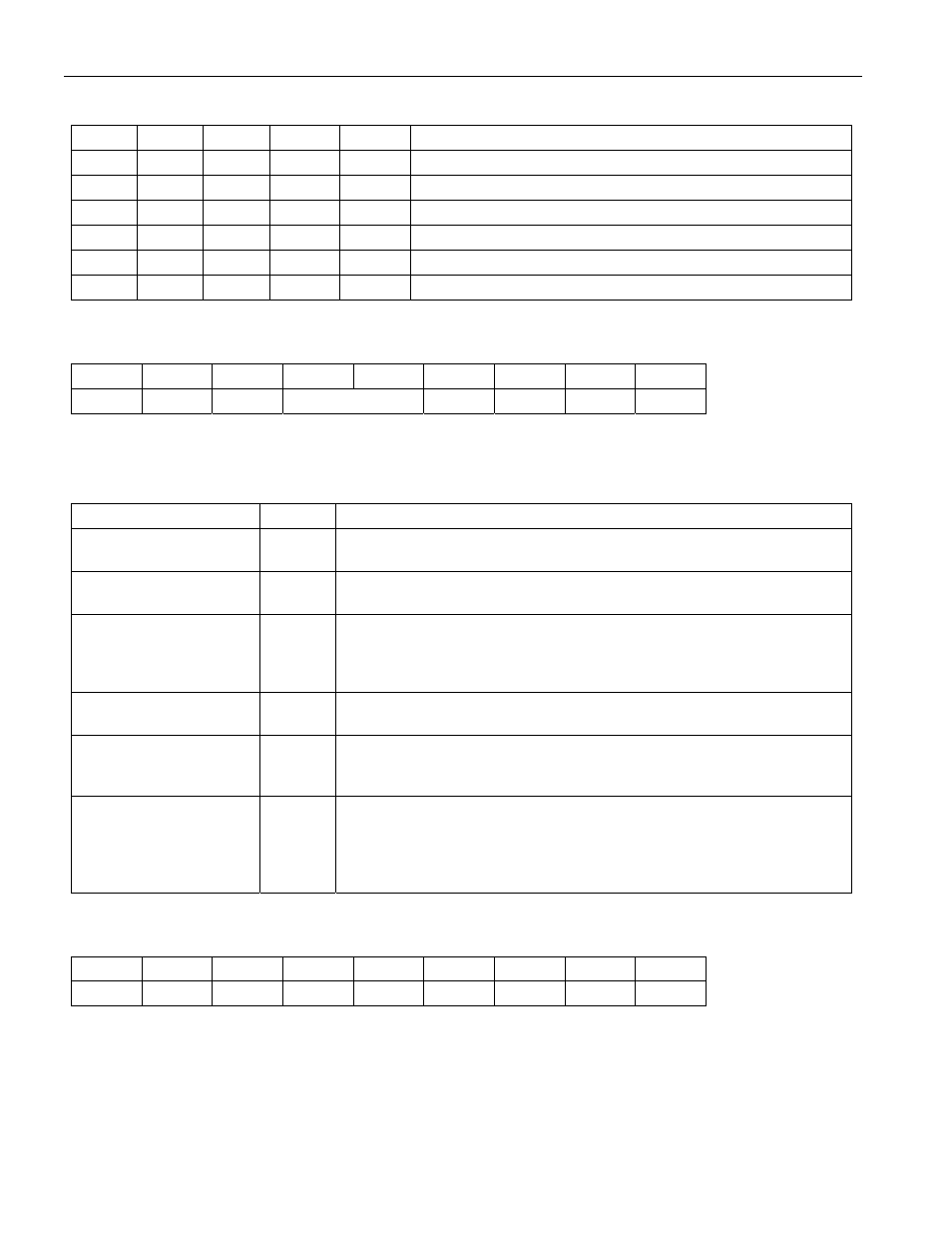

Table 1. Alarm Frequency Control

DY/DT AM4 AM3 AM2 AM1

ALARM

OCCURRENCE

X X X X 1

Every

second

X

X

X

1

0

Every minute, when the seconds match

X

X

1

0

0

Every hour, when minutes and seconds match

X

1

0

0

0

Every day, when hours, minutes, and seconds match

1

0

0

0

0

Every week, when day, hours, minutes, and seconds match

0

0

0

0

0

Every month, when date, hours, minutes, and seconds match

Multifunction Control/Setup Register

ADDR

b7 b6 b5 b4 b3 b2 b1 b0

134h

0 BME

BTRP WDOS

WDE

OSCE

CAE

There is general read and write access to this address. Bit 7 always reads 0; it cannot be written to 1. This register

is reset to 00h when the battery voltage ramps up. See Figure 5 for the use of the CAE, WDE, WDOS, and BME

bits in the generation of the ALMZ, RSTZ, and WDOZ signals.

BIT DESCRIPTION

BIT(S)

DEFINITION

CAE: Clock Alarm

Enable

b0

Enable/disable control of the

RTC

/Calendar alarm.

Legend

:

0 Î disabled (power-on default); 1 Î enabled

OSCE: RTC Oscillator

Enable

b1

Run/halt control of the

RTC

’s 32KHz oscillator

Legend

:

0 Î halted (power-on default); 1 Î running

WDE: Watchdog Enable

b2

Enable/disable control of the watchdog and its alarm.

Legend

:

0 Î disabled (power-on default); 1 Î enabled

The watchdog timer is reset by changing WDE from 0 to 1, V

CC

ramp up

(Power-on reset) or applying a positive pulse at the WDI pin.

WDOS: Watchdog

Output Selection

b3

Pin selection for watchdog alarm signaling.

Legend

:

0 Î WDOZ pin (power-on default); 1 Î ALMZ pin

BTRP: Battery Monitor

Trip Point

b5:b4

Selection of the nominal Battery Monitor Trip Point voltage.

Legend

:

00b Î 1.75V (power-on default); 01b Î 2.00V;

10b

Î

2.25V; 11b Î 2.50V

BME: Battery Monitor

Enable

b6

Enable/disable control of the Battery Monitor and its alarm.

Legend

:

0 Î disabled (power-on default); 1 Î enabled

The battery test takes place a) after BME changes to 1, b) after V

CC

ramps up, c) every hour on the hour. The

RTC

must be running (OSCE

= 1) for the battery monitor to function.

Alarm and Status Register

ADDR

b7 b6 b5 b4 b3 b2 b1 b0

135h

0 BATA

WPZV

POR

BOR

CLKA

WDA

RST

There is general read access to this address; writing clears all bits to 0. Bit 7 always reads 0. See Figure 5 for the

use of the CLKA, WDA, and BATA bits in the generation of the ALMZ, RSTZ, and WDOZ signals.