Rainbow Electronics DS28DG02 User Manual

Page 12

DS28DG02: 2kb SPI EEPROM with PIO, RTC, Reset, Battery Monitor, and Watchdog

12 of 33

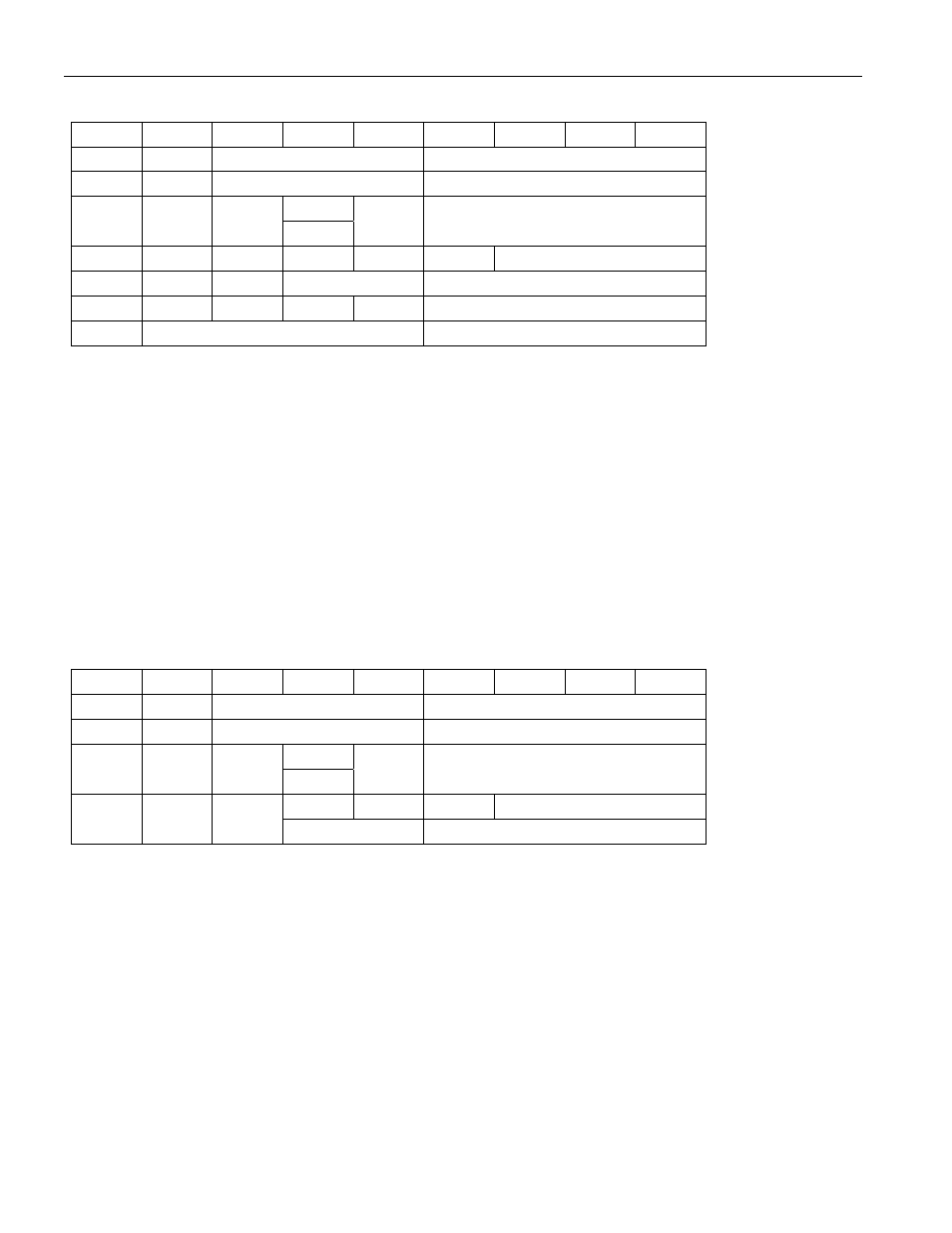

RTC and Calendar Registers

ADDR

b7 b6 b5 b4 b3 b2 b1 b0

129h

0

10 Seconds

Single Seconds

12Ah

0

10 Minutes

Single Minutes

10hrs

12Bh

0 12/24

A/P

10hrs Single

Hours

12Ch

0 0 0 0 0

Day

of

Week

12Dh

0

0

10 Date

Single Date

12Eh

0 0 0

Single

Months

12Fh

10 Years

Single Years

There is general read and write access to these addresses. Bits shown as 0 cannot be written to 1. The RTC and

calendar registers are reset to 00h when the battery voltage ramps up. Writes take effect immediately. To prevent

unexpected increments during write access, first update the seconds; this creates a 1s window to finish updating

the RTC/Calendar registers without any carryover from the Seconds register. Whenever the DS28DG02 receives a

SPI Read command, the RTC and Calendar registers are copied to a buffer. When during a read access the

address counter points to the RTC/Calendar registers, data from the buffer is transmitted. To obtain most accurate

RTC data, start reading at the Seconds register.

The number representation of the RTC/Calendar registers is BCD (binary-coded decimal). The RTC can run in the

12-hour AM/PM and the 24-hour mode. The “12/24” bit (bit 6 of address 12Bh) defines the mode. For 12-hour

AM/PM mode, set this bit to 1; bit 5 of address 12Bh then indicates AM (0b) or PM (1b). In the 24-hour mode, bit 5

and bit 4 together indicate the multiple of 10 hours. The Day of Week register counts from 1 to 7. The calendar

logic is designed to automatically compensate for leap years. For every year value that is either 00 or a multiple of

4 the device will add a 29th of February. This will work correctly up to (but not including) the year 2100.

RTC

Alarm Registers

ADDR

b7 b6 b5 b4 b3 b2 b1 b0

130h

AM1

10 Seconds

Single Seconds

131h

AM2

10 Minutes

Single Minutes

10hrs

132h

AM3 12/24

A/P

10hrs Single

Hours

0 0 0

Day

of

Week

133h

AM4 DY/DT

10 Date

Single Date

There is general read and write access to these addresses. Bits shown as 0 cannot be written to 1. The

RTC

Alarm

registers are reset to 00h when the battery voltage ramps up. To generate an alarm, there must be a match

between Alarm registers and RTC registers. Alarm register addresses 130h to 132h correspond to RTC register

addresses 129h to 12Bh; bits 6:0 participate in the comparison. The lower 6 bits of register address 133h

correspond to 12Ch if DY/DT is 1 and to 12Dh if DY/DT is 0; the upper 2 bits of this register do not participate in the

comparison. The control bits AM1, AM2, AM3, and AM4 determine the frequency of the alarm, as shown in Table

1. When the alarm occurs, the CLKA bit of the Alarm and Status register at address 135h changes to 1. The RTC

must be running for the device to generate RTC alarms (OSCE at address 134h = 1).