Table 2-1 – Xilinx 1000BASE-X User Manual

Page 32

32

Ethernet 1000BASE-X PCS/PMA or SGMII v9.1

UG155 March 24, 2008

Chapter 2: Core Architecture

R

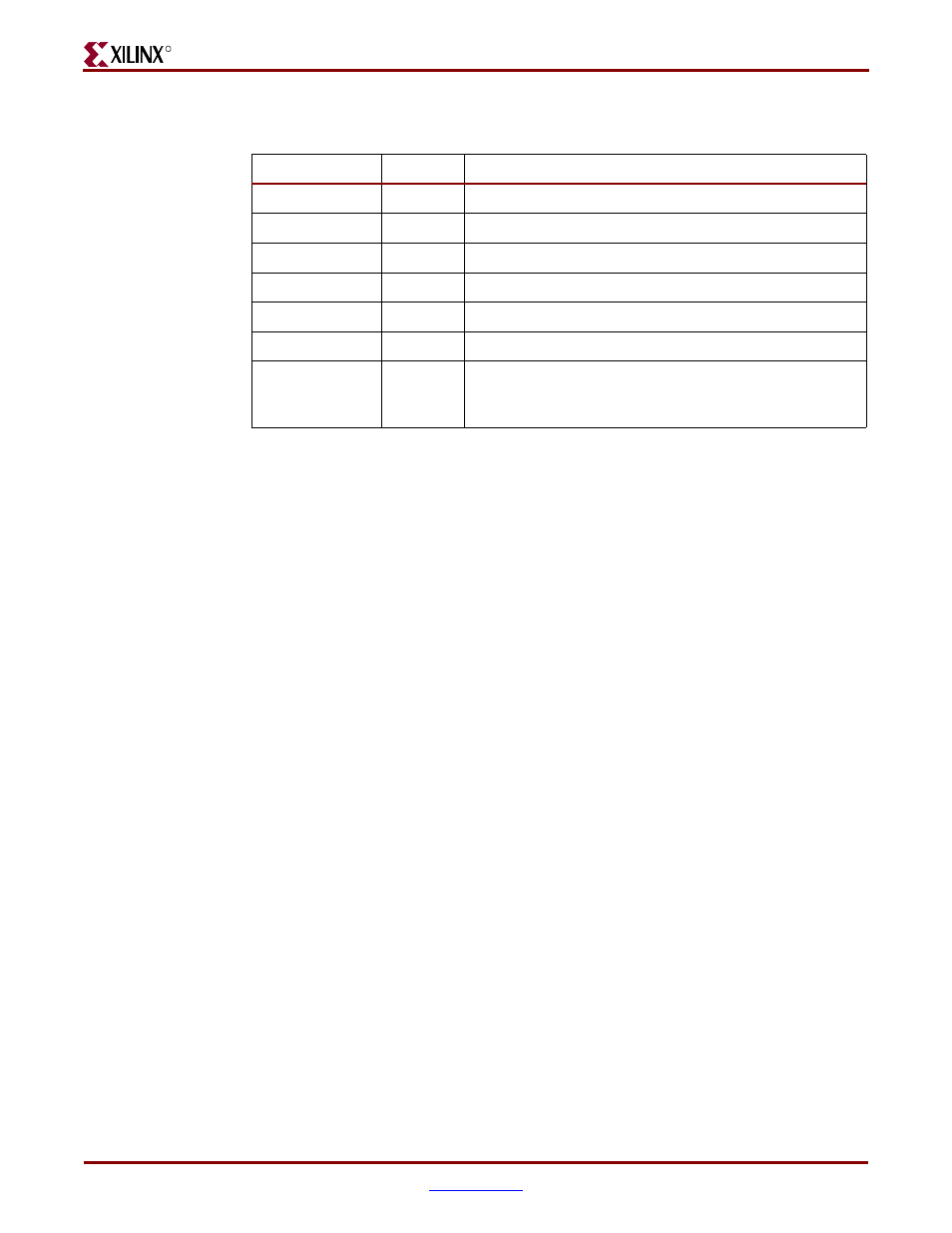

Table 2-1:

GMII Interface Signal Pinout

Signal

Direction

Description

gmii_txd[7:0]

1

1. When the Transmitter Elastic Buffer is present these signals are synchronous to gmii_tx_clk. When the

Transmitter Elastic Buffer is omitted, see Note 2.

Input

GMII Transmit data from MAC.

gmii_tx_en

Input

GMII Transmit control signal from MAC.

gmii_tx_er

Input

GMII Transmit control signal from MAC.

gmii_rxd[7:0]

2

2. These signals are synchronous to the core’s internal 125 MHz reference clock. This is userclk2 when the

core is used with the RocketIO transceiver; gtx_clk when the core is used with TBI.

Output

GMII Received data to MAC.

gmii_rx_dv

Output

GMII Received control signal to MAC.

gmii_rx_er

Output

GMII Received control signal to MAC.

gmii_isolate

Output

IOB Tri-state control for GMII Isolation. Only of use

when implementing an External GMII as illustrated by

the example design HDL.