Virtex-4 rocketio mgts for 1000base-x constraints, Figure 12-1, Clock period constraints – Xilinx 1000BASE-X User Manual

Page 164

164

Ethernet 1000BASE-X PCS/PMA or SGMII v9.1

UG155 March 24, 2008

Chapter 12: Constraining the Core

R

Virtex-4 RocketIO MGTs for 1000BASE-X Constraints

The constraints defined in this section are implemented in the UCF for the example

designs delivered with the core. Sections from the UCF are copied into the following

descriptions to serve as examples and should be studied in conjunction with the HDL

source code for the example design. See also

“Virtex-4 FX Devices” in Chapter 7

Clock Period Constraints

The clock txoutclk is provided by the MGT for use in the FPGA fabric. It is connected to

global clock routing to produce the usrclk2 signal. This is the main 125 MHz clock used

by all core logic and must be constrained.

DCLK

is a clock with a frequency between 25 and 50 MHz, which must be provided to the

Dynamic Reconfiguration Port and to the calibration block of the MGT. In the example

design, this is constrained to 50 MHz.

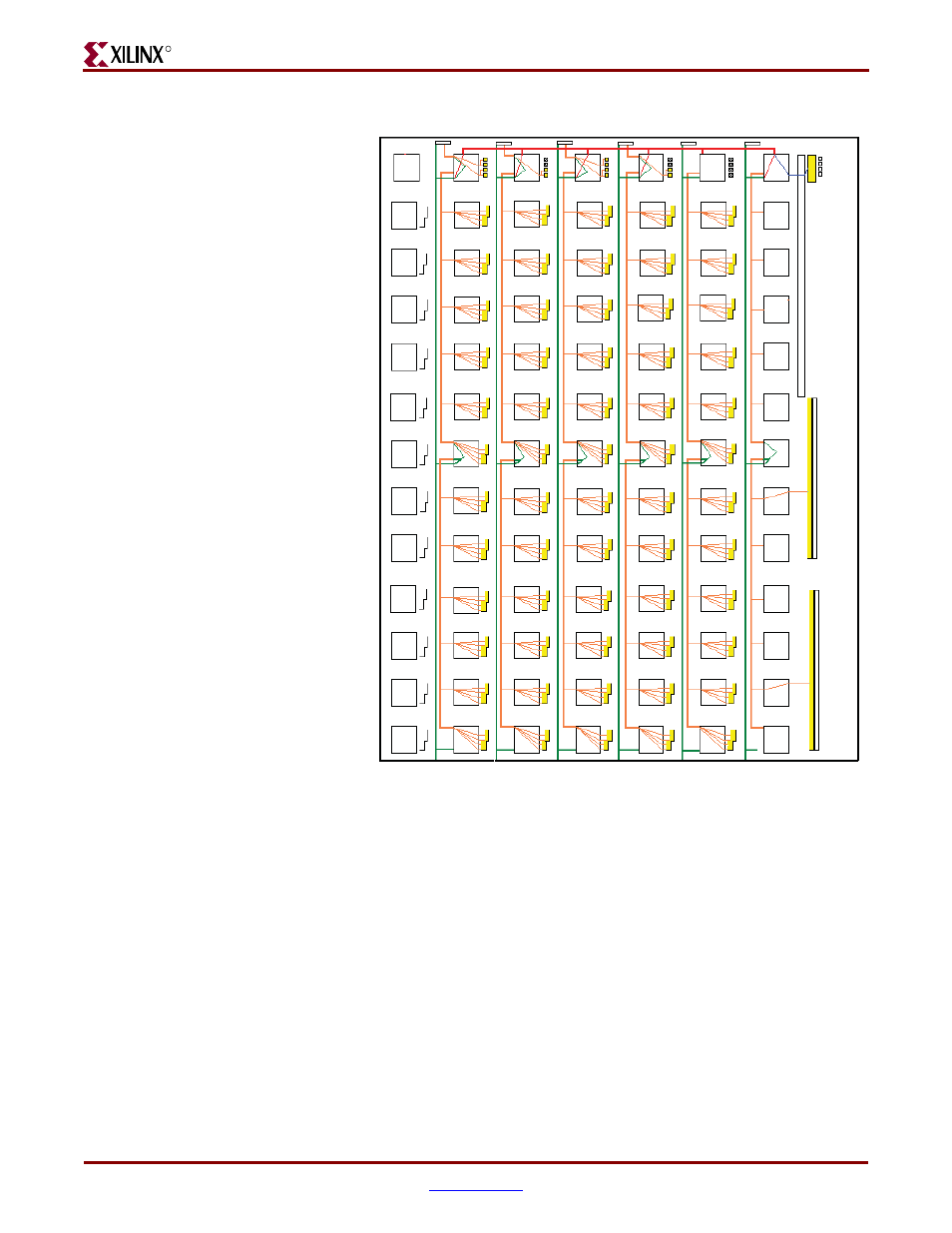

Figure 12-1:

Local Clock Place and Route for Top MGT

Legend:

Green - Vertical

Long Line

Orange - VFULLHEX

Red - HFULLHEX

Yellow - BRAM/

Multiplier/Slices/

MGT