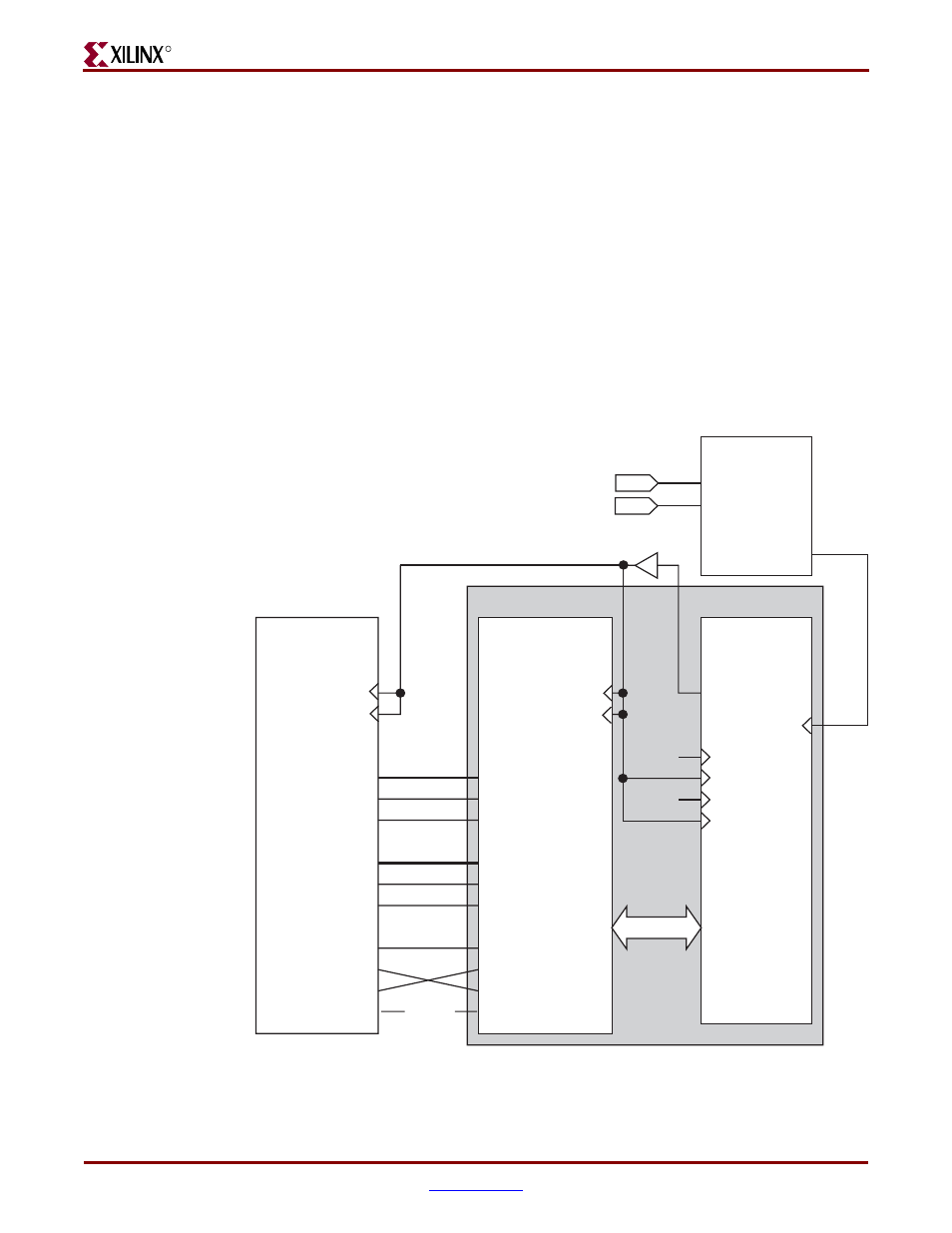

Figure 13-3, Virtex-4 devices, Chapter 13: interfacing to other cores – Xilinx 1000BASE-X User Manual

Page 182

182

Ethernet 1000BASE-X PCS/PMA or SGMII v9.1

UG155 March 24, 2008

Chapter 13: Interfacing to Other Cores

R

•

If both cores have been generated with the optional management interface, the MDIO

port can be connected up to that of the 1-Gigabit Ethernet MAC core, allowing the

MAC to access the embedded configuration and status registers of the Ethernet

1000BASE-X PCS/PMA or SGMII core.

•

Due to the embedded Receiver Elastic Buffer in the MGT, the entire GMII is

synchronous to a single-clock domain. Therefore, userclk2 is used as the 125 MHz

reference clock for both cores, and the transmitter and receiver logic of the 1-Gigabit

Ethernet MAC core now operate in the same clock domain.

Virtex-4 Devices

illustrates the connections and clock management logic required to interface

the Ethernet 1000BASE-X PCS/PMA or SGMII core (when used in 1000BASE-X mode) to

the 1-Gigabit Ethernet MAC core.

Figure 13-3:

1-Gigabit Ethernet MAC Extended to Include 1000BASE-X PCS and

PMA Using a Virtex-4 MGT

1-Gigabit Ethernet

MAC

LogiCORE

gmii_rx_clk

gmii_rxd[7:0]

gmii_rx_dv

gmii_rx_er

gmii_txd[7:0]

gmii_tx_en

gmii_tx_er

gtx_clk

mdc

mdio_in

mdio_out

mdio_tri

Ethernet 1000BASE-X

PCS/PMA or SGMII

LogiCORE

gmii_rxd[7:0]

gmii_rx_dv

gmii_rx_er

gmii_txd[7:0]

gmii_tx_en

gmii_tx_er

mdc

mdio_in

mdio_out

mdio_tri

Virtex-4

GT11

RocketIO

no

connection

userclk

userclk2

RocketIO I/F

IPAD

IPAD

brefclkn

(250 MHz)

Virtex-4

GT11CLK_MGT

MGTCLKP

MGTCLKN

SYNCLK1OUT

brefclkp

(250 MHz)

REFCLK1

userclk2

(125 MHz)

TXUSRCLK

TXUSRCLK2

RXUSRCLK

RXUSRCLK2

synclk1

(250MHz

‘0’

‘0’

BUFG

TXOUTCLK1

component_name_block

(Block Level from example design)