Figure 8-5, The si – Xilinx 1000BASE-X User Manual

Page 104

104

Ethernet 1000BASE-X PCS/PMA or SGMII v9.1

UG155 March 24, 2008

Chapter 8: SGMII / Dynamic Standards Switching with RocketIO Transceivers

R

.

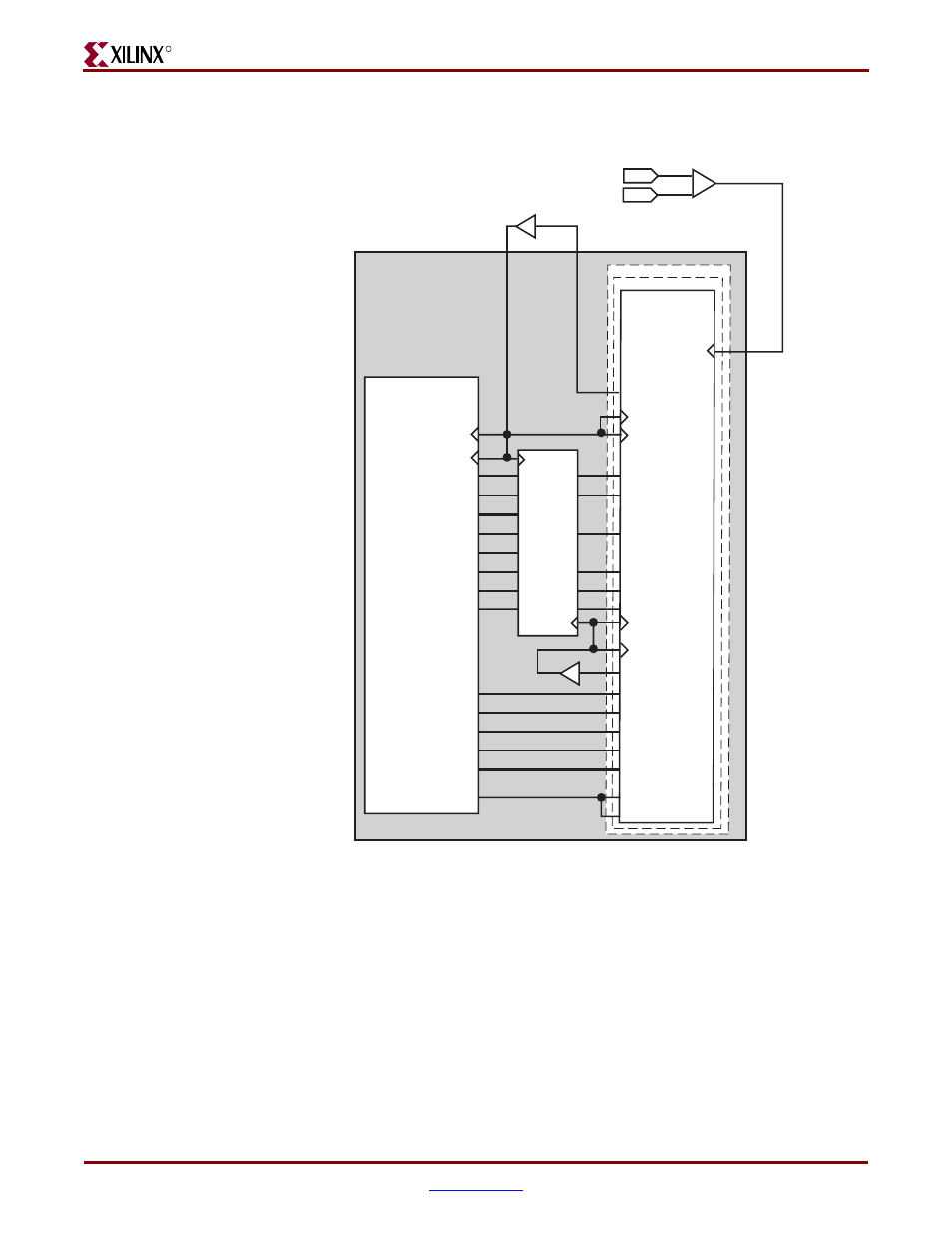

Figure 8-5:

SGMII Connection to a Virtex-5 RocketIO GTP Transceiver

Ethernet 1000BASE-X

PCS/PMA or SGMII

LogiCORE

Virtex-5

GTP

RocketIO

(used)

TXUSRCLK0

TXUSRCLK20

RXUSRCLK20

userclk

userclk2

rxbufstatus[1:0]

rxchariscomma

rxcharisk

rxclkcorcnt[2:0]

rxdata[7:0]

rxrundisp

powerdown

txchardispmode

txchardispval

txcharisk

txdata[7:0]

enablealign

RXCHARISCOMMA0

RXCHARISK0

RXDATA0[7:0]

RXRUNDISP0

POWERDOWN0

TXCHARDISPMODE0

TXCHARDISPVAL0

TXCHARISK0

TXDATA[07:0]

RXENPCOMMAALIGN0

RXENMCOMMAALIGN0

RXDISPERR0

rxdisperr

CLKIN

REFCLKOUT

FPGA

fabric

Rx

Elastic

Buffer

RXNOTINTABLE0

rxnotintable

BUFR

RXRECCLK0

userclk2 (125MHz)

BUFG

component_name_block

(Block Level from

example design)

RXUSRCLK0

clkin

(125MHz)

IBUFGDS

IPAD

brefclkp

IPAD

brefclkn

rocketio_wrapper_gtp_tile

rocketio_wrapper_gtp