Table 9-28 – Xilinx 1000BASE-X User Manual

Page 144

144

Ethernet 1000BASE-X PCS/PMA or SGMII v9.1

UG155 March 24, 2008

Chapter 9: Configuration and Status

R

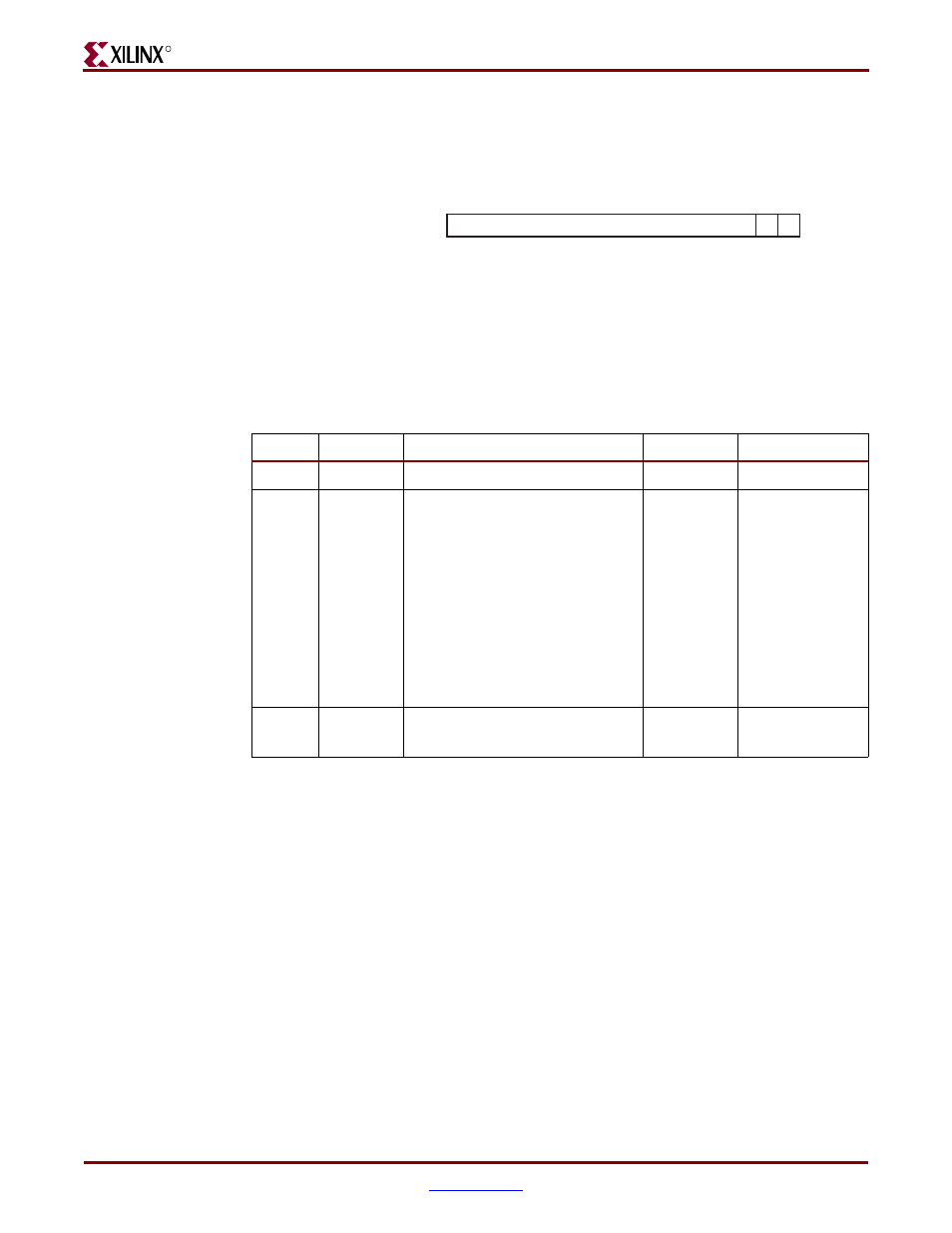

Register 16: SGMII Auto-Negotiation Interrupt Control

MDIO Register 16: SGMII Auto-Negotiation Interrupt Control

Table 9-28:

SGMII Auto-Negotiation Interrupt Control (Register 16)

Bit(s)

Name

Description

Attributes

Default Value

16.15:2

Reserved

Always return 0s

returns 0s

00000000000000

16.1

Interrupt

Status

1 = Interrupt is asserted

0 = Interrupt is not asserted

If the interrupt is enabled, this bit is

asserted on completion of an Auto-

Negotiation cycle across the SGMII

link; it is only cleared by writing ‘0’

to this bit.

If the Interrupt is disabled, the bit is

set to ‘0.’

NOTE: The an_interrupt port of the

core is wired to this bit.

read/

write

0

16.0

Interrupt

Enable

1 = Interrupt enabled

0 = Interrupt disabled

read/

write

1

15

0

Reg 16

RESER

VED

1

2

INTERR

UPT ST

A

TUS

INTERR

UPT ENABLE