Both 1000base-x and sgmii standards, Table 9-34, Register 15: sgmii extended status – Xilinx 1000BASE-X User Manual

Page 150

150

Ethernet 1000BASE-X PCS/PMA or SGMII v9.1

UG155 March 24, 2008

Chapter 9: Configuration and Status

R

Register 15: SGMII Extended Status

Both 1000BASE-X and SGMII Standards

describes register 17, the vendor-specific Standard Selection Register. This

register is only present when the core is generated with the capability to dynamically

switch between 1000BASE-X and SGMII standards. See

“Select Standard” in Chapter 3

When this Register is configured to perform the 1000BASE-X standard, Registers 0 to 16

should be interpreted as per

“1000BASE-X Standard Using the Optional Auto-

or

“1000BASE-X Standard Without the Optional Auto-Negotiation.”

When this Register is configured to perform the SGMII standard, Registers 0 to 16 should

be interpreted as per

“SGMII Standard Using the Optional Auto-Negotiation,”

Standard without the Optional Auto-Negotiation.”

This register may be written to at any

time. See

Chapter 11, “Dynamic Switching of 1000BASE-X and SGMII Standards”

information.

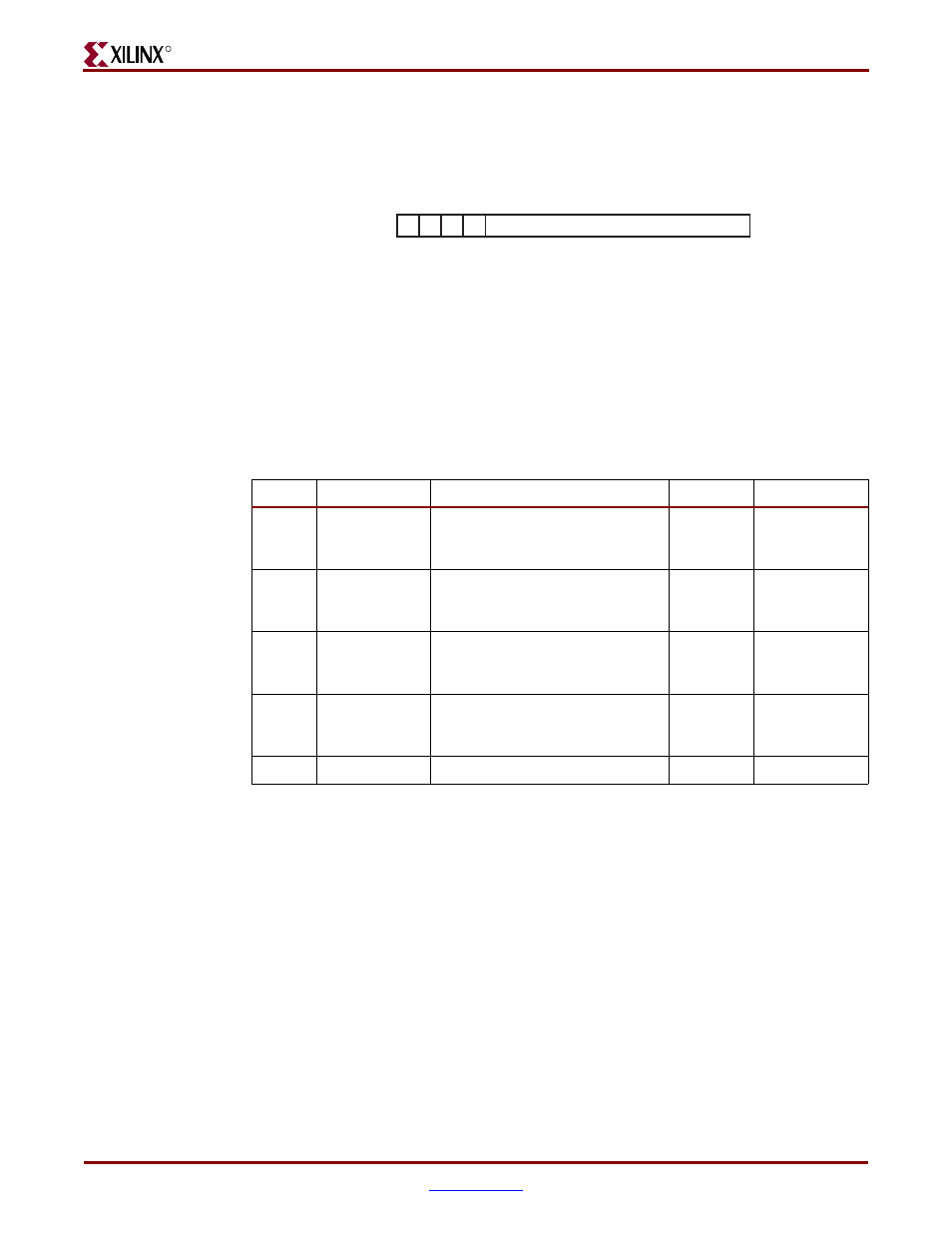

MDIO Register 15: SGMII Extended Status

Table 9-34:

SGMII Extended Status Register (Register 15)

Bit(s)

Name

Description

Attributes

Default Value

15.15

1000BASE-X

Full Duplex

Always returns a ‘1’ for this bit since

1000BASE-X Full Duplex is

supported

returns 1

1

15.14

1000BASE-X

Half Duplex

Always returns a ‘0’ for this bit since

1000BASE-X Half Duplex is not

supported

returns 0

0

15.13

1000BASE-T

Full Duplex

Always returns a ‘0’ for this bit since

1000BASE-T Full Duplex is not

supported

returns 0

0

15.12

1000BASE-T

Half Duplex

Always returns a ‘0’ for this bit since

1000BASE-T Half Duplex is not

supported

returns 0

0

15:11:0

Reserved

Always return 0s

returns 0s

000000000000

1000BASE-X FULL DUPLEX

1000BASE-X HALF DUPLEX

1000BASE-T FULL DUPLEX

15 14 13 12 11

0

Reg 15

RESER

VED

1000BASE-T HALF DUPLEX