Table 9-14, Register 0: control register – Xilinx 1000BASE-X User Manual

Page 130

130

Ethernet 1000BASE-X PCS/PMA or SGMII v9.1

UG155 March 24, 2008

Chapter 9: Configuration and Status

R

Register 0: Control Register

MDIO Register 0: Control Register

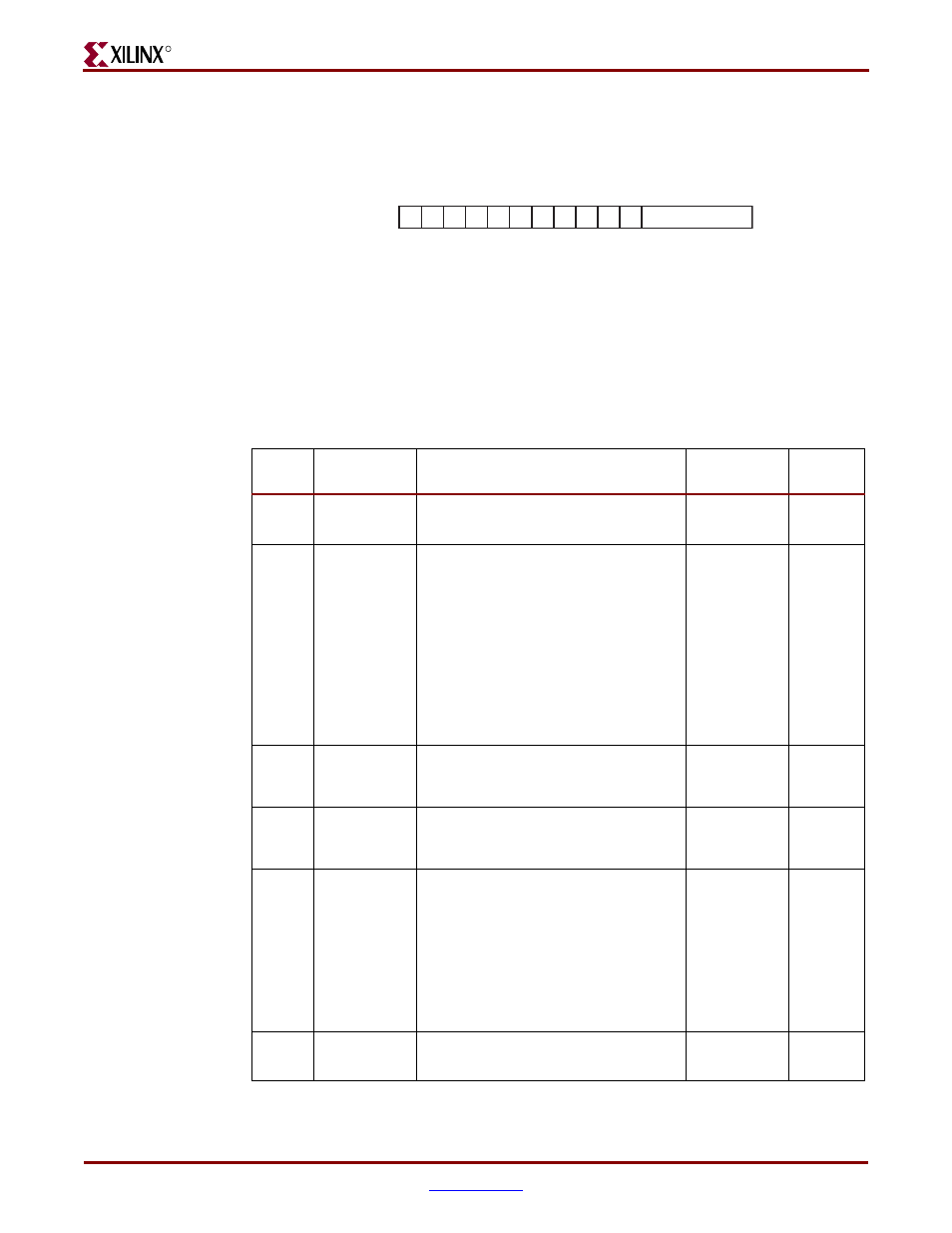

Table 9-14:

Control Register (Register 0)

Bit(s)

Name

Description

Attributes

Default

Value

0.15

Reset

1 = PCS/PMA reset

0 = Normal Operation

read/write

self clearing

0

0.14

Loopback

1 = Enable Loopback Mode

0 = Disable Loopback Mode

When used with a RocketIO transceiver,

the core is placed in internal loopback

mode.

With the TBI version, Bit 1 is connected to

ewrap

. When set to ‘1’ indicates to the

external PMA module to enter loopback

mode.

See

.

read/write

0

0.13

Speed

Selection

(LSB)

Always returns a 0 for this bit. Together

with bit 0.6, speed selection of 1000 Mbps

is identified.

returns 0

0

0.12

Auto-

Negotiation

Enable

Ignore this bit because Auto-Negotiation

is not included.

read/ write

1

0.11

Power Down

1 = Power down

0 = Normal operation

With the PMA option, when set to ’1’ the

RocketIO transceiver is placed in a low-

power state. This bit requires a reset (see

bit 0.15) to clear.

With the TBI version this register bit has

no effect.

read/ write

0

0.10

Isolate

1 = Electrically Isolate PHY from GMII

0 = Normal operation

read/write

1

RESET

LOOPBA

CK

A

U

T

O-NEG ENABLE

REST

AR

T A

U

T

O-NEG

RESER

VED

PO

WER DO

WN

SPEED

SPEED

15 14 13 12 11 10

7

6

5

0

Reg 0

ISOLA

TE

9

8

DUPLEX MODE

COLLISION TEST

4

UNIDIRECTIONAL ENABLE