Figure 8-3, Shows – Xilinx 1000BASE-X User Manual

Page 100

100

Ethernet 1000BASE-X PCS/PMA or SGMII v9.1

UG155 March 24, 2008

Chapter 8: SGMII / Dynamic Standards Switching with RocketIO Transceivers

R

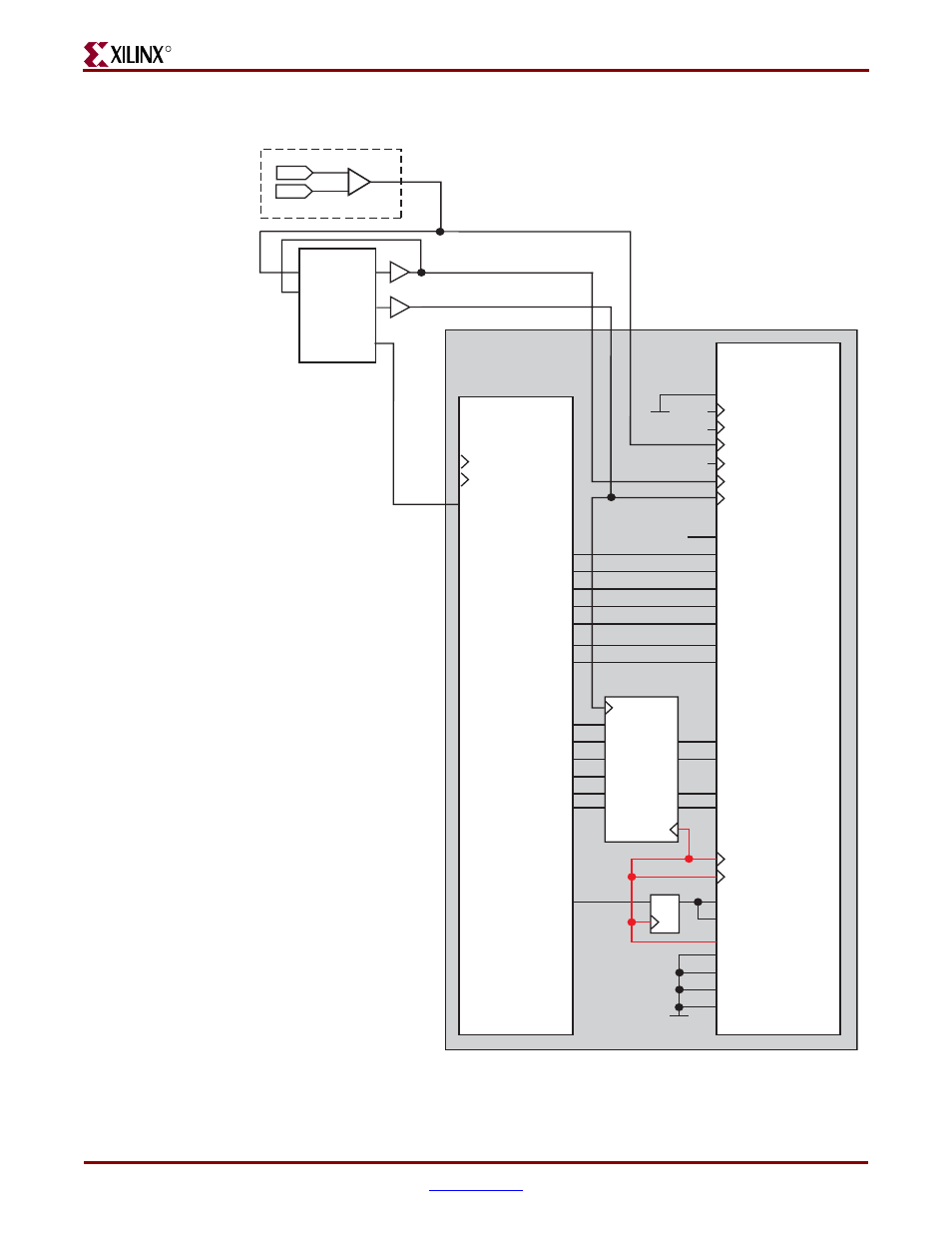

Figure 8-3:

SGMII Connection to a Virtex-II Pro RocketIO Transceiver

Ethernet 1000BASE-X

PCS/PMA or SGMII

LogiCORE

Virtex-II Pro

RocketIO

(GT_CUSTOM)

BREFCLK2

TXUSRCLK

TXUSRCLK2

userclk

userclk2

dcm_locked

powerdown

txchardispmode

txchardispval

txcharisk

txdata[7:0]

enablealign

LOOPBACK[1:0]

POWERDOWN

TXCHARDISPMODE

TXCHARDISPVAL

TXCHARISK

TXDATA[7:0]

BREFCLK

REFCLK2

REFCLK

REFCLKSEL

NC

NC

NC

GND

ENPCOMMAALIGN

ENMCOMMAALIGN

D

Q

RXRECCLK

RXPOLARITY

TXPOLARITY

TXFORCECRCERR

TXINHIBIT

GND

GND

rxbufstatus[1:0]

rxchariscomma

rxcharisk

rxclkcorcnt[2:0]

rxdata[7:0]

rxdisperr

mgt_tx_reset

mgt_rx_reset

RXRESET

TXRESET

RXCHARISCOMMA[1:0]

RXCHARISK[1:0]

RXDATA[15:0]

RXDISPERR[1:0]

RXUSRCLK

RXUSRCLK2

FPGA

fabric

Rx

Elastic

Buffer

local

clock

routing

DCM

CLKIN CLK0

FB

BUFG

CLK2X180

BUFG

userclk (62.5MHz)

userclk2 (125MHz)

IPAD

IBUFGDS

IOB LOGIC

brefclkp

IPAD

brefclkn

brefclk (62.5MHz)

LOCKED

component_name_block

(Block Level from

example design)