1 control register (ctrlr), Section 4.1 – Texas Instruments TMS320DM357 User Manual

Page 82

4.1

Control Register (CTRLR)

Registers

www.ti.com

Table 16. Universal Serial Bus (USB) Registers (continued)

Offset

Acronym

Register Description

Section

546h

PERI_RXCSR

Control Status Register for Peripheral Receive Endpoint

(peripheral mode)

HOST_RXCSR

Control Status Register for Host Receive Endpoint

(host mode)

548h

RXCOUNT

Number of Bytes in Host Receive endpoint FIFO

54Ah

HOST_TXTYPE

Sets the operating speed, transaction protocol and peripheral

endpoint number for the host Transmit endpoint.

54Bh

HOST_TXINTERVAL

Sets the polling interval for Interrupt/ISOC transactions or the

NAK response timeout on Bulk transactions for host Transmit

endpoint.

54Ch

HOST_RXTYPE

Sets the operating speed, transaction protocol and peripheral

endpoint number for the host Receive endpoint.

54Dh

HOST_RXINTERVAL

Sets the polling interval for Interrupt/ISOC transactions or the

NAK response timeout on Bulk transactions for host Receive

endpoint.

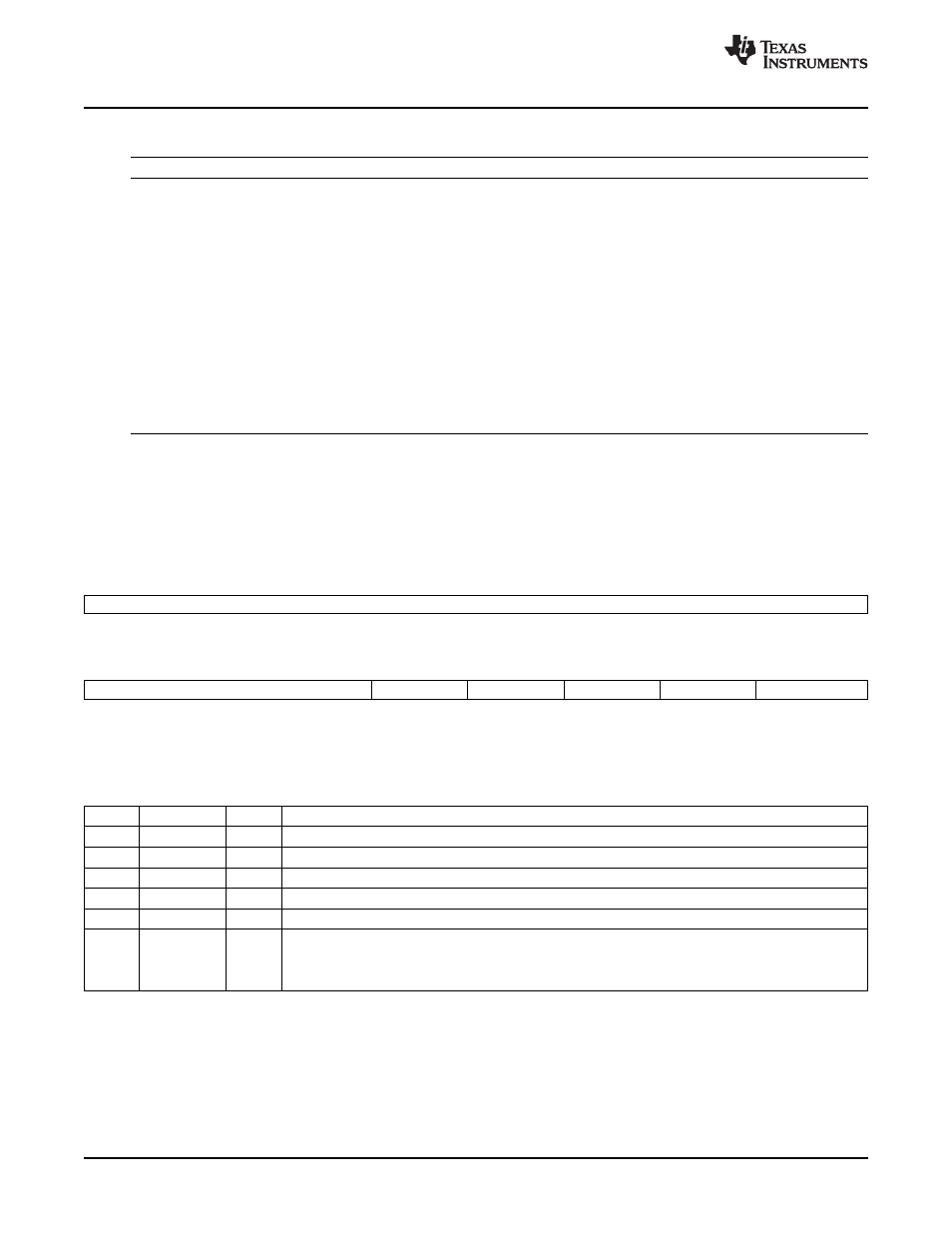

The Control Register (CTRLR) is shown in

and described in

Figure 16. Control Register (CTRLR)

31

16

Reserved

R-0

15

5

4

3

2

1

0

Reserved

RNDIS

UINT

Reserved

CLKFACK

RESET

R-0

R/W-0

R/W-0

R-0

R/W-0

W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 17. Control Register (CTRLR) Field Descriptions

Bit

Field

Value

Description

31-5

Reserved

0

Reserved

4

RNDIS

0-1

RNDIS mode enable.

3

UINT

0-1

USB non-PDR interrupt enable.

2

Reserved

0

Reserved

1

CLKFACK

0-1

Clock stop fast ACK enable.

0

RESET

Soft reset.

0

1

Writing a 1 starts a module reset.

Universal Serial Bus (USB) Controller

82

SPRUGH3 – November 2008