Testmode), Descriptions, Section 4.55 – Texas Instruments TMS320DM357 User Manual

Page 118

4.55 Register to Enable the USB 2.0 Test Modes (TESTMODE)

Registers

www.ti.com

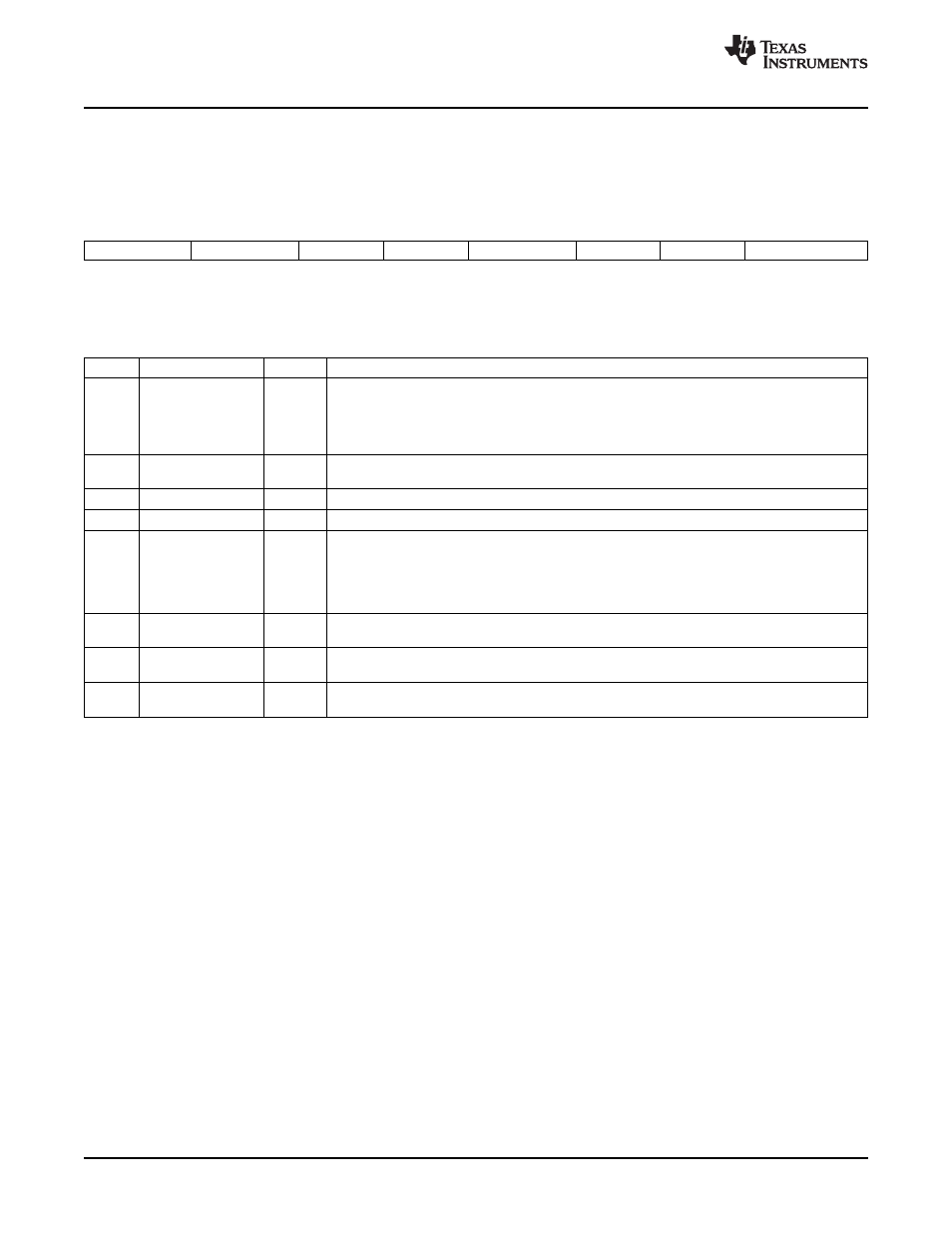

The Register to Enable the USB 2.0 Test Modes (TESTMODE) is shown in

and described in

Figure 70. Register to Enable the USB 2.0 Test Modes (TESTMODE)

7

6

5

4

3

2

1

0

FORCE_HOST

FIFO_ACCESS

FORCE_FS

FORCE_HS

TEST_PACKET

TEST_K

TEST_J

TEST_SE0_NAK

R/W-0

W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 71. Register to Enable the USB 2.0 Test Modes (TESTMODE) Field Descriptions

Bit

Field

Value

Description

7

FORCE_HOST

0-1

Set this bit to forcibly put the USB controller into Host mode when SESSION bit is set,

regardless of whether it is connected to any peripheral. The controller remains in Host mode

until the Session bit is cleared, even if a device is disconnected. And if the FORCE_HOST but

remains set, it will re-enter Host mode next time the SESSION bit is set. The operating speed is

determined using the FORCE_HS and FORCE_FS bits.

6

FIFO_ACCESS

0-1

Set this bit to transfer the packet in EP0 Tx FIFO to EP0 Receive FIFO. It is cleared

automatically.

5

FORCE_FS

0-1

Set this bit to force the USB controller into full-speed mode when it receives a USB reset.

4

FORCE_HS

0-1

Set this bit to force the USB controller into high-speed mode when it receives a USB reset.

3

TEST_PACKET

0-1

Set this bit to enter the Test_Packet test mode. In this mode, the USB controller repetitively

transmits a 53-byte test packet on the bus, the form of which is defined in the Universal Serial

Bus Specification Revision 2.0.

Note: The test packet has a fixed format and must be loaded into the Endpoint 0 FIFO before

the test mode is entered.

2

TEST_K

0-1

Set this bit to enter the Test_K test mode. In this mode, the USB controller transmits a

continuous K on the bus.

1

TEST_J

0-1

Set this bit to enter the Test_J test mode. In this mode, the USB controller transmits a

continuous J on the bus.

0

TEST_SE0_NAK

0-1

Set this bit to enter the Test_SE0_NAK test mode. In this mode, the USB controller remains in

high-speed mode, but responds to any valid IN token with a NAK.

Universal Serial Bus (USB) Controller

118

SPRUGH3 – November 2008