72 configuration data register (configdata), Section 4.72, Table 87 – Texas Instruments TMS320DM357 User Manual

Page 132

4.72 Configuration Data Register (CONFIGDATA)

Registers

www.ti.com

Table 87. Receive Interval Register (Host mode only) (HOST_RXINTERVAL) Field Descriptions

Bit

Field

Value

Description

7-0

POLINTVL_NAKLIMIT

0-FFh

For Interrupt and Isochronous transfers, defines the polling interval for the

currently-selected transmit endpoint For Bulk endpoints, this register sets the number of

frames/microframes after which the endpoint should timeout on receiving a stream of NAK

responses. There is a transmit Interval register for each configured transmit endpoint

(except Endpoint 0). In each case the value that is set defines a number of

frames/microframes (High Speed transfers), as follows:

Transfer Type Speed Valid values (m) Interpretation

Interrupt Low Speed or Full Speed 1 - 255 Polling interval is m frames

High Speed 1 - 16 Polling interval is 2

(—1)

microframes

Isochronous Full Speed or High Speed 1 - 16 Polling interval is 2

(—1)

frames/microframes

Bulk Full Speed or High Speed 2 - 16 NAK Limit is 2

(—1)

frames/microframes

Note: A value of 0 or 1 disables the NAK timeout function

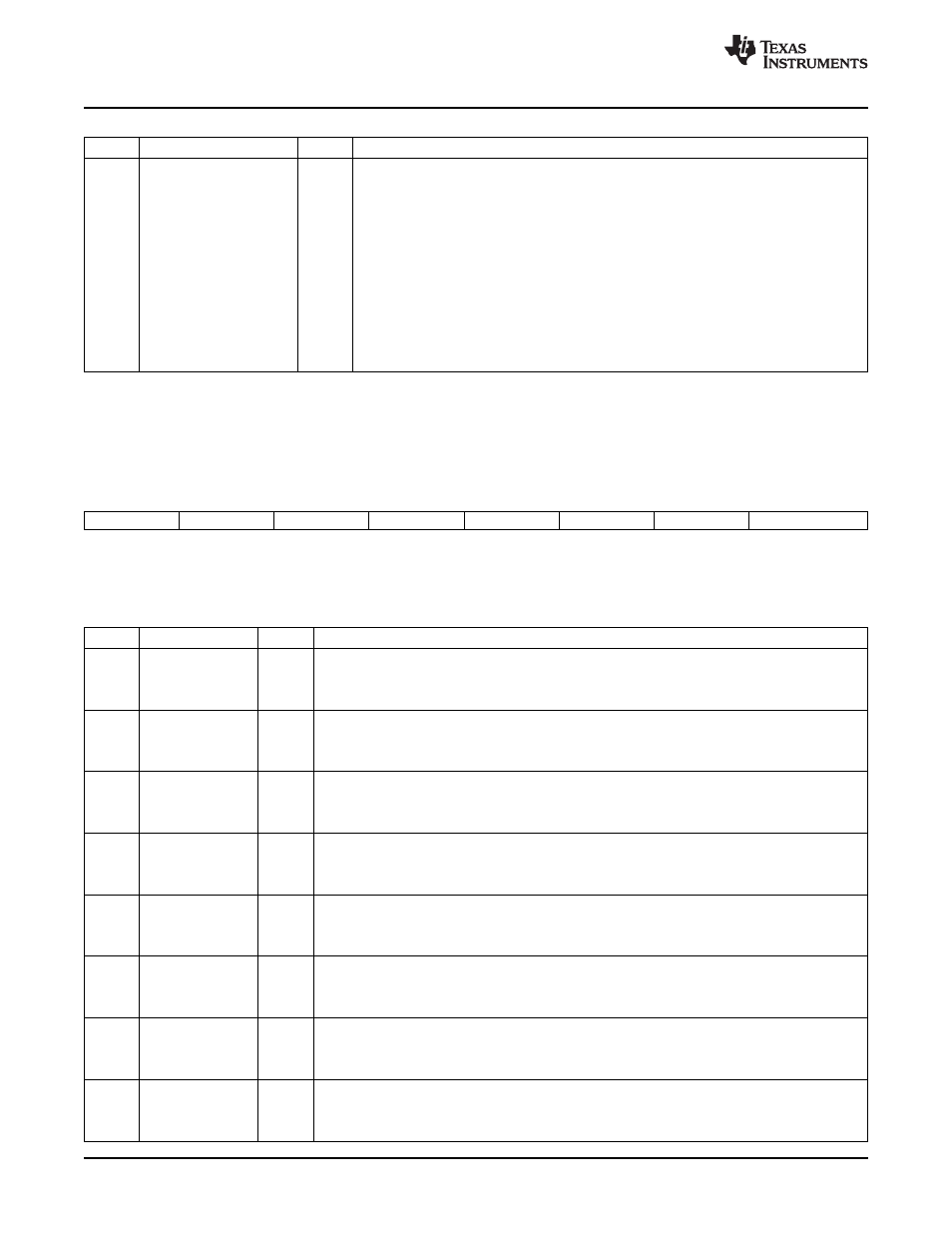

The configuration data register (CONFIGDATA) is shown in

and described in

.

Figure 87. Configuration Data Register (CONFIGDATA)

7

6

5

4

3

2

1

0

MPRXE

MPTXE

BIGENDIAN

HBRXE

HBTXE

DYNFIFO

SOFTCONE

UTMIDATAWIDTH

R-0

R-0

R-0

R-0

R-0

R-1

R-1

R-0

LEGEND: R = Read only; -n = value after reset

Table 88. Configuration Data Register (CONFIGDATA) Field Descriptions

Bit

Field

Value

Description

7

MPRXE

Indicates automatic amalgamation of bulk packets.

0

Automatic amalgamation of bulk packets is not selected.

1

Automatic amalgamation of bulk packets is selected.

6

MPTXE

Indicates automatic splitting of bulk packets.

0

Automatic splitting of bulk packets is not selected.

1

Automatic splitting of bulk packets is selected.

5

BIGENDIAN

Indicates endian ordering.

0

Little-endian ordering is selected.

1

Big-endian ordering is selected.

4

HBRXE

Indicates high-bandwidth Rx ISO endpoint support.

0

High-bandwidth Rx ISO endpoint support is not selected.

1

High-bandwidth Rx ISO endpoint support is selected.

3

HBTXE

Indicates high-bandwidth Tx ISO endpoint support.

0

High-bandwidth Tx ISO endpoint support is not selected.

1

High-bandwidth Tx ISO endpoint support is selected.

2

DYNFIFO

Indicates dynamic FIFO sizing.

0

Dynamic FIFO sizing option is not selected.

1

Dynamic FIFO sizing option is selected.

1

SOFTCONE

Indicates soft connect/disconnect.

0

Soft connect/disconnect option is not selected

1

Soft connect/disconnect option is selected

0

UTMIDATAWIDTH

Indicates selected UTMI data width.

0

8 bits

1

16 bits

Universal Serial Bus (USB) Controller

132

SPRUGH3 – November 2008