29 receive buffer count 3 register (rbufcnt3), Rbufcnt3), Tcppidmastatew0) – Texas Instruments TMS320DM357 User Manual

Page 101: Descriptions, Section 4.29, Section 4.30

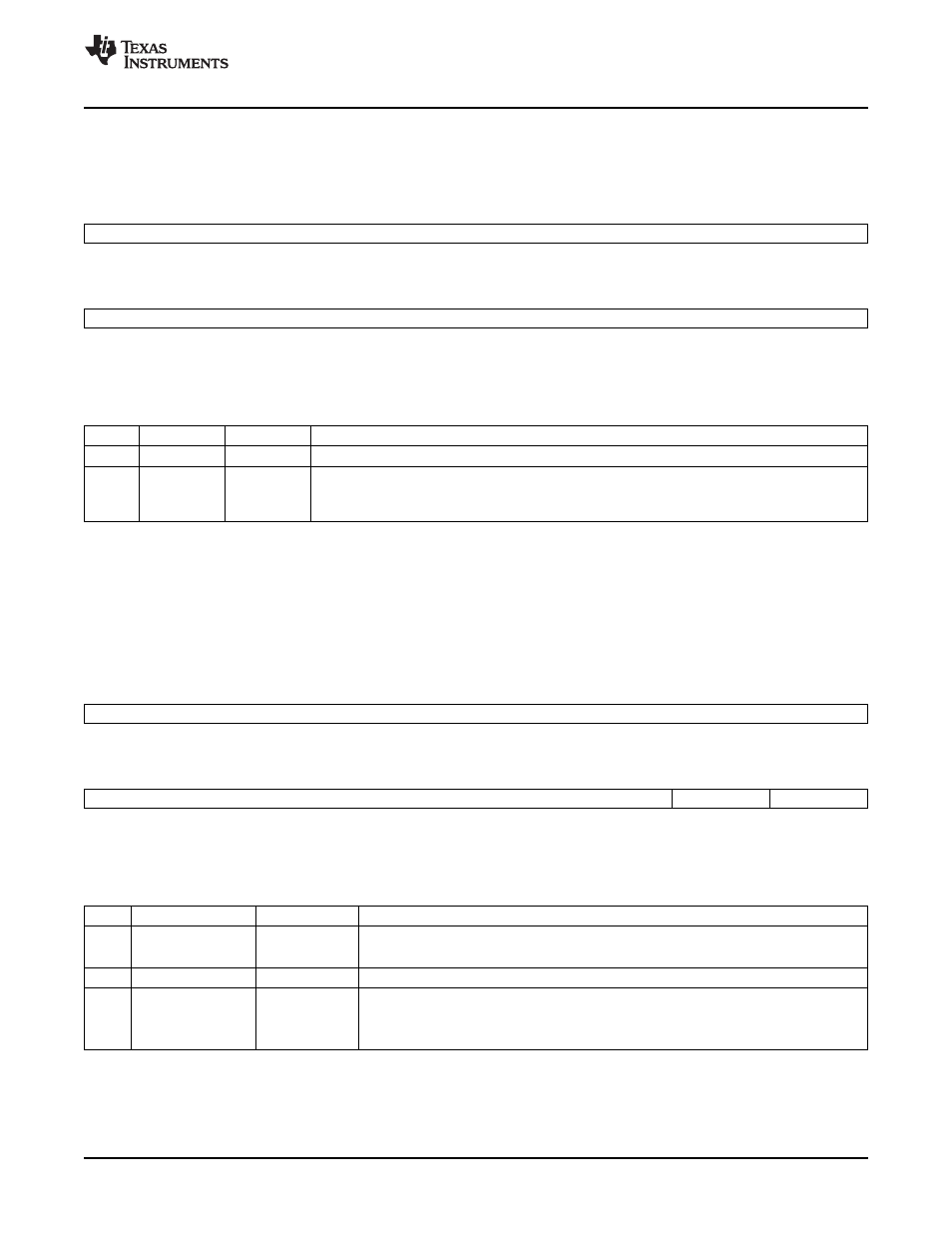

4.29 Receive Buffer Count 3 Register (RBUFCNT3)

4.30 Transmit CPPI DMA State Word 0 (TCPPIDMASTATEW0)

www.ti.com

Registers

The Receive Buffer Count 3 Register (RBUFCNT3) is shown in

and described in

Figure 44. Receive Buffer Count 3 Register (RBUFCNT3)

31

16

Reserved

R-0

15

0

BUFCNT

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 45. Receive Buffer Count 3 Register (RBUFCNT3) Field Descriptions

Bit

Field

Value

Description

31-16

Reserved

0

Reserved

15-0

BUFCNT

0-FFFFh

Receive CPPI Buffer Count 0

The current count of CPPI buffers in Receive channel 3 queue. Writes add to current value (not

overwrite). The DMA requires a minimum of 3 RX buffers to operate.

The Transmit CPPI DMA State Word 0 (TCPPIDMASTATEW0) is shown in

and described in

Figure 45. Transmit CPPI DMA State Word 0 (TCPPIDMASTATEW0)

31

16

TXQ_HEAD_PTR

R/W-0

15

2

1

0

TXQ_HEAD_PTR

Reserved

IN_PACKET

R/W-0

R-0

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 46. Transmit CPPI DMA State Word 0 (TCPPIDMASTATEW0) Field Descriptions

Bit

Field

Value

Description

31-2

TXQ_HEAD_PTR

0-3FFF FFFFh

TX Queue Head Pointer

30-bit pointer to 32-bit aligned descriptor at the head of the high priority TX queue

1

Reserved

0

Reserved

0

IN_PACKET

Flag indicating the DMA is in the middle of processing a packet

0

Not currently in packet

1

Currently in packet

SPRUGH3 – November 2008

Universal Serial Bus (USB) Controller

101