Chart – Texas Instruments TMS320DM357 User Manual

Page 34

TX mode

Write

MaxP bytes

to FIFO

Last

packet

?

No

Yes

Set TxPktRdy

and set DataEnd

state −> IDLE

Return

TxPktRdy

Set

USB Controller Host and Peripheral Modes Operation

www.ti.com

3.1.1.5.2

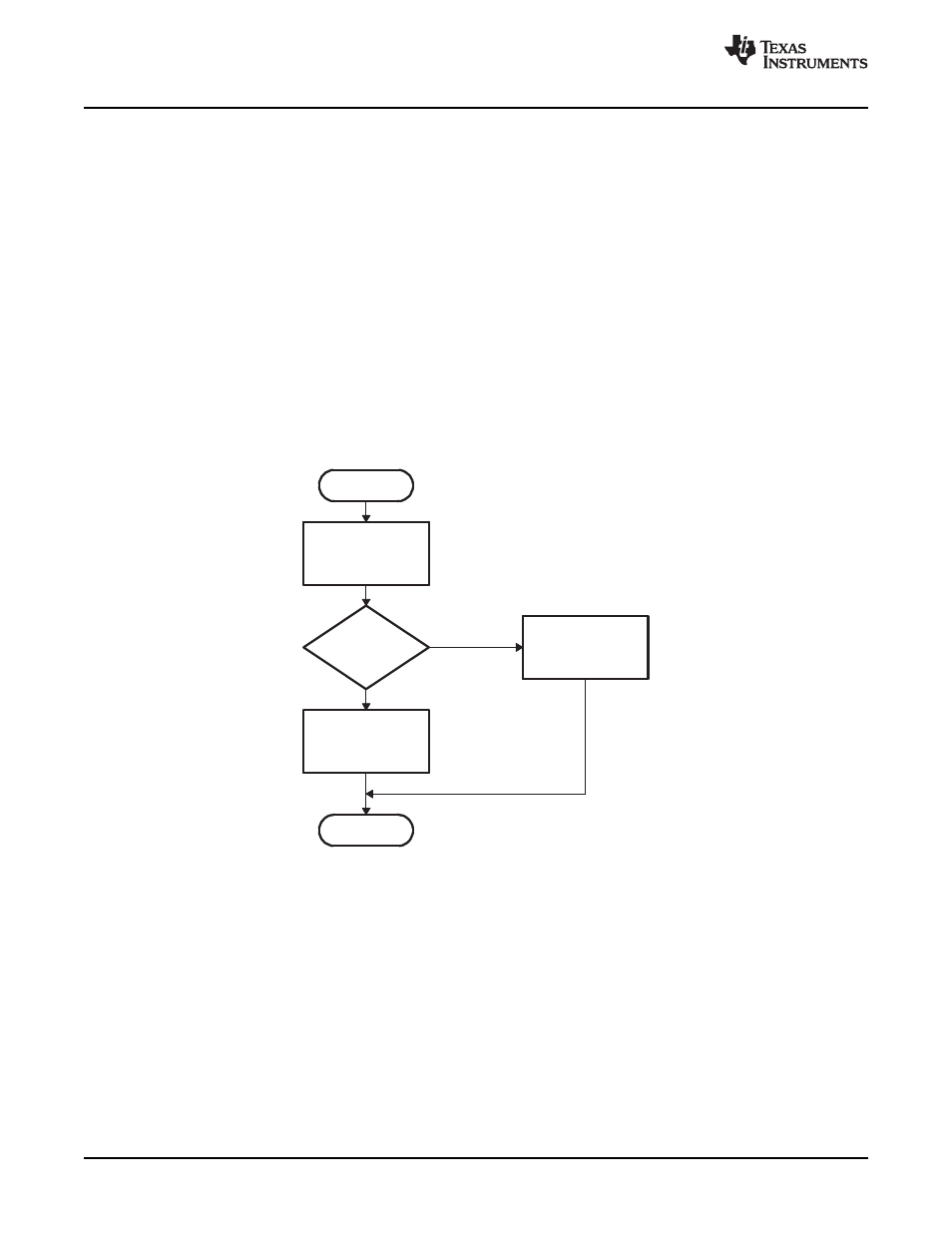

TX Mode

When the endpoint is in TX state all arriving IN tokens need to be treated as part of a data phase until the

required amount of data has been sent to the host. If either a SETUP or an OUT token is received while

the endpoint is in the TX state, this will cause a SetupEnd condition to occur as the core expects only IN

tokens. See

Three events can cause TX mode to be terminated before the expected amount of data has been sent:

1. The host sends an invalid token causing a SETUPEND condition (bit 4 of PERI_CSR0 set).

2. The software sends a packet containing less than the maximum packet size for endpoint 0.

3. The software sends an empty data packet.

Until the transaction is terminated, the software simply needs to load the FIFO when it receives an

interrupt that indicates a packet has been sent from the FIFO. (An interrupt is generated when

TXPKTRDY is cleared.)

When the software forces the termination of a transfer (by sending a short or empty data packet), it should

set the DATAEND bit of PERI_CSR0 (bit 3) to indicate to the core that the data phase is complete and

that the core should next receive an acknowledge packet.

Figure 7. TX Mode Flow Chart

34

Universal Serial Bus (USB) Controller

SPRUGH3 – November 2008