Section 4.63 – Texas Instruments TMS320DM357 User Manual

Page 126

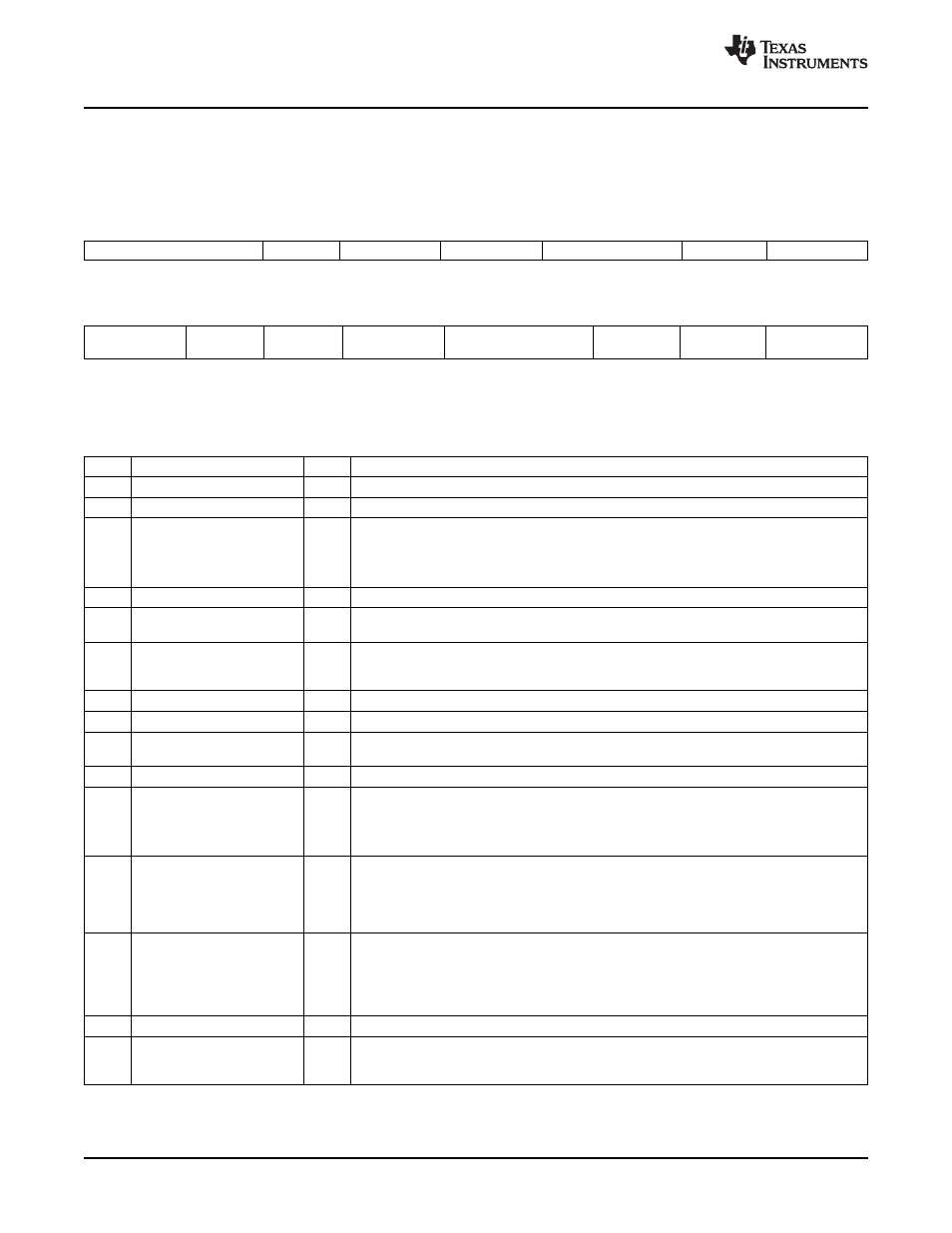

4.63 Control Status Register for Host Receive Endpoint (HOST_RXCSR)

Registers

www.ti.com

The Control Status Register for Host Receive Endpoint (HOST_RXCSR) is shown in

and

described in

Figure 78. Control Status Register for Host Receive Endpoint (HOST_RXCSR)

15

14

13

12

11

10

9

8

Reserved

DMAEN

DISNYET

DMAMODE

DATATOGWREN

DATATOG

Reserved

R-0

R/W-0

R/W-0

R/W-0

W-0

R/W-0

R-0

7

6

5

4

3

2

1

0

CLRDATATOG

RXSTALL

REQPKT

FLUSHFIFO

DATAERR_NAK

ERROR

FIFOFULL

RXPKTRDY

TIMEOUT

W-0

R/W-0

R/W-0

W-0

R-0

R/W-0

R-0

R/W-0

LEGEND: R/W = Read/Write; R = Read only; W = Write only; -n = value after reset

Table 79. Control Status Register for Host Receive Endpoint (HOST_RXCSR) Field Descriptions

Bit

Field

Value

Description

15-14

Reserved

0

Reserved

13

DMAEN

0-1

Set this bit to enable the DMA request for the Receive endpoints.

12

DISNYET

0-1

Set this bit to disable the sending of NYET handshakes. When set, all successfully received

Receive packets are ACKED including at the point at which the FIFO becomes full.

Note: This bit only has any effect in high-speed mode, in which mode it should be set for all

Interrupt endpoints.

11

DMAMODE

0

This bit should always be cleared to 0.

10

DATATOGWREN

0-1

Set this bit to enable the DATATOG bit to be written. This bit is automatically cleared once

the new value is written to DATATOG.

9

DATATOG

0-1

When read, this bit indicates the current state of the Receive EP data toggle. If

DATATOGWREN is high, this bit can be written with the required setting of the data toggle.

If DATATOGWREN is low, any value written to this bit is ignored.

8

Reserved

0

Reserved

7

CLRDATATOG

0-1

Set this bit to reset the endpoint data toggle to 0.

6

RXSTALL

0-1

When a STALL handshake is received, this bit is set and an interrupt is generated. You

should clear this bit.

5

REQPKT

0-1

Set this bit to request an IN transaction. It is cleared when RXPKTRDY is set.

4

FLUSHFIFO

0-1

Set this bit to flush the next packet to be read from the endpoint Receive FIFO. The FIFO

pointer is reset and the RXPKTRDY bit is cleared.

Note: FLUSHFIFO has no effect unless RXPKTRDY is set. Also note that, if the FIFO is

double-buffered, FLUSHFIFO may need to be set twice to completely clear the FIFO.

3

DATAERR_NAKTIMEOUT

0-1

When operating in ISO mode, this bit is set when RXPKTRDY is set if the data packet has

a CRC or bit-stuff error and cleared when RXPKTRDY is cleared. In Bulk mode, this bit will

be set when the Receive endpoint is halted following the receipt of NAK responses for

longer than the time set as the NAK Limit by the RXINTERVAL register. You should clear

this bit to allow the endpoint to continue.

2

ERROR

0-1

The USB controller sets this bit when 3 attempts have been made to receive a packet and

no data packet has been received. You should clear this bit. An interrupt is generated when

the bit is set.

Note: This bit is only valid when the transmit endpoint is operating in Bulk or Interrupt

mode. In ISO mode, it always returns zero.

1

FIFOFULL

0-1

This bit is set when no more packets can be loaded into the Receive FIFO.

0

RXPKTRDY

0-1

This bit is set when a data packet has been received. You should clear this bit when the

packet has been unloaded from the Receive FIFO. An interrupt is generated when the bit is

set.

Universal Serial Bus (USB) Controller

126

SPRUGH3 – November 2008